# Chapter 4 Other Information

#### Chapter 4 Other Information

#### **§**l Display

#### 1.1. Display Settings

MultiFonts CP/M for the QX-10 supports both green and color display monitors. Since different hardware is used in each of these, it is also necessary to set the display controller in different modes. When the system uses a green monitor in the non-MFBASIC normal mode, BIOS sets the display controller in the mixed character/graphics mode and the entire screen is set in the character display area. When the system uses a green monitor in the non-MFBASIC MF mode or MFBASIC mode, BIOS sets the display controller in the mixed character/graphics mode and the entire screen is set in the graphic display area.

In the case of a color monitor, the display controller is set in the graphic mode for all modes of operation (non-MFBASIC normal and MF modes, and MFBASIC mode).

The table below summarizes the I/O port numbers and data output to set the display controller in the different display modes. The mode settings are made with the scroll command.

| Mode                | Green                                                    | monitor                              | Color monitor                                                  |

|---------------------|----------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|

| I/O port            | Non-MFBASIC Non-MFBASIC MF normal mode mode/MFBASIC mode |                                      | Non-MFBASIC normal<br>mode/non-MFBASIC MF<br>mode/MFBASIC mode |

| Command<br>039H     | 070н                                                     | 070н                                 | 070н                                                           |

| Parameter 1<br>038H | 0 (Lower byte of display address)                        | 0 (Lower byte of<br>display address) | 0 (Lower byte of<br>display address)                           |

| Parameter 2<br>038H | 0 (Upper byte of display address)                        | 0 (Upper byte of display address)    | 0 (Upper byte of<br>display address)                           |

| Parameter 3<br>038H | 0 or 0F0H                                                | ОГОН                                 | ОГОН                                                           |

| Parameter 4<br>038H | 019н ог 03Fн                                             | 07FH                                 | 03Fн                                                           |

Parameters 1 and 2 specify the starting address for display; i.e., the VRAM address which is displayed in the upper left corner of the screen. When parameters 1 and 2 are incremented by 1 (this is done by a 16-bit logical operation) and the commands and parameters (parameters 1 to 4) are written to the I/O ports again, results differ according to mode as follows. For a green monitor in the non-MFBASIC normal mode, the character in the upper left corner is erased and all other characters are moved back one position. A new character then moves into the bottom right corner of the screen. For a green monitor in the non-MFBASIC MF mode or MFBASIC mode or a color monitor in any mode, the 16-dot area at the upper left corner of the screen is erased and all other portions of the screen are moved back a corresponding amount. New data then moves into the 16-dot area at the bottom right corner of the

screen.

Thus, the scroll command both determines the screen mode and scrolls data.

All characters are displayed as bit images when a green monitor is used in the mixed character/graphics mode and the graphic section is specified or when a color monitor is used. See the description of the CONOUT routine in Chapter 1 for details.

A green monitor is provided with the QX-10 as standard equipment; however, a color monitor can also be used when the optional color monitor interface board is installed. Since BIOS also provides support for color monitors, no changes need be made in MultiFonts CP/M. Differentiation between the green and color monitors and specification of the display colors for the color monitor is as follows.

<Differentiation between green and color monitors>

When a green monitor is connected, the value present at I/O port 02CH is 0FEH, and when a color monitor is connected, the value present is 0FDH.

<Display color specification for color monitors>

Any of eight different colors--black (no color), blue, red, green, purple, light blue, yellow, and white--can be displayed. However, colors other than blue, red, and green are displayed by combining two or more of these three basic colors.

Purple - Displayed using blue and red

Light blue - Displayed using blue and green

Yellow - Displayed using red and green

White - Displayed using blue, red, and green

The colors blue, red, and green are specified by setting one bit of the corresponding I/O port to "1". (Results are not assured if more than one bit is set to "1".)

I/O port 02DH <-- 01B (01H) - Blue

I/O port 02DH <-- 010B (02H) - Green

I/O port 02DH <-- 0100B (04H) - Red

Once a color has been specified, that specification remains effective until the next specification is made. The color specification is invalid when a green monitor is used. when the screen is not zoomed.

#### 1.2 Zoom Function

The  $\mu PD7220$  is used as the display controller in the QX-10. This controller is equipped with a zoom function. The zoom function makes it possible to magnify characters for display. However, this change in size is not reflected in hard copies taken of the display; when a hard copy is made, characters appear the same as

Zooming is done by outputting commands to I/O ports as shown below.

```

IN

A, (038H)

MIND

6

XOR

4

;7220 BUFFER EMPTY?

JR

; NO.

NZ, $-6

; ZOOM COMMAND.

LD

A. 046H

OUT

(039H),A

LD

A,010H

; ZOOM PARAMETER.

(038H),A

OUT

LD

A. 1

DUT

(03AH),A

```

Here, I/O port 039H is the  $\mu PD7220$  command port and 038H is the parameter and status port. The zoom command is 046H; after this command has been output, it is followed by outputting the magnification to the parameter port. The magnification must also be output to port 03AH.

The zoom magnification can be set to any value from 1 to 16. The value which is output to I/O port 038H is equal to (ratio - 1) x 16, and that which is output to port 03AH is equal to (ratio - 1).

The command sequence for magnifying characters by 10 is as follows.

```

.

LD A,046H

OUT (039H),A ;COMMAND.

LD A,090H

OUT (038H),A ;PARAMETER 1 x 10

LD A,09H

OUT (03AH),A ;PARAMETER 2 x 10

```

The upper left corner of the display is used as the origin for zooming. Thus, characters are enlarged from the top left corner toward the bottom right. The reason for using the upper left corner of the display as the origin is that processing becomes quite complicated if the origin is placed at the center; i.e., it becomes necessary to change the display address for the upper left corner each time the zoom function is used. This could be done using the scroll command.

The scroll command and its parameters are as follows.

| K                   |                                   |                                     |                                                                |  |  |

|---------------------|-----------------------------------|-------------------------------------|----------------------------------------------------------------|--|--|

| Mode                | Green                             | Green monitor                       |                                                                |  |  |

| I/O port            | Non-MFBASIC<br>normal mode        | Non-MFBASIC MF<br>mode/MFBASIC mode | Non-MFBASIC normal<br>mode/non-MFBASIC MF<br>mode/MFBASIC mode |  |  |

| Command<br>039H     | 070н                              | 070н                                | 070н                                                           |  |  |

| Parameter l<br>038H | 0 (Lower byte of display address) | 0 (Lower byte of display address)   | 0 (Lower byte of display address)                              |  |  |

| Parameter 2<br>038H | 0 (Upper byte of display address) | 0 (Upper byte of display address)   | 0 (Upper byte of<br>display address)                           |  |  |

| Parameter 3<br>038H | ОГОН                              | ОГОН                                | ОГОН                                                           |  |  |

| Parameter 4<br>038H | 03FH                              | 07 <b>гн</b>                        | 03FH                                                           |  |  |

See the discussion of the CONOUT routine in Chapter 1 concerning display addresses and display modes.

Although the display address can be changed independently of the zoom function, BIOS would have no way of knowing that a change had been made. Therefore, subsequent character display might not be performed properly the next time the CONOUT routine is called. Thus, if the display address is changed, it must be restored (or the screen must be cleared) before calling CONOUT. The display address is saved as two bytes in SPOS (address OFE70H) in the BIOS common data area, and can be restored by outputting that value to an I/O port with the scroll command.

BIOS support is not provided when the zoom function is used, and cannot be utilized again until the original character size is restored. This is done by setting a magnification ratio of 1.

Magnification of characters for display by the zoom function is done entirely by hardware, and no software considerations are necessary. The effect is the same as if the display were viewed through a magnifying glass. Although portions of the image extending beyond the edge of the screen are not visible, all data in VRAM can be brought into view by executing the scroll command to move the display address up, down, left, or right. Again, results are not assured if CONOUT is called for display.

However, the CONOUT routine can be used to output an escape sequence to clear the screen. In this case, it is the user's responsibility to restore the zoom magnification to the original ratio.

#### §2 Memory Banks

#### 2.1 Using the User Banks

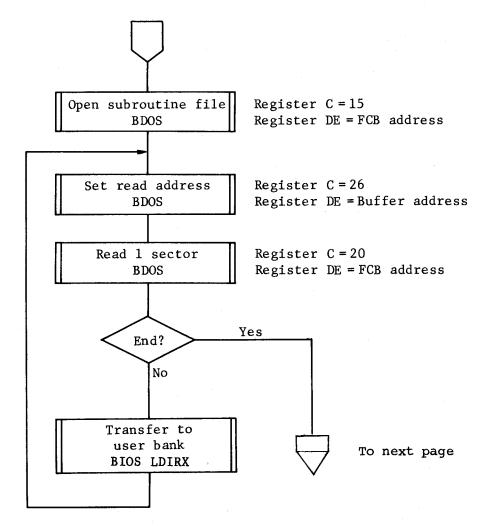

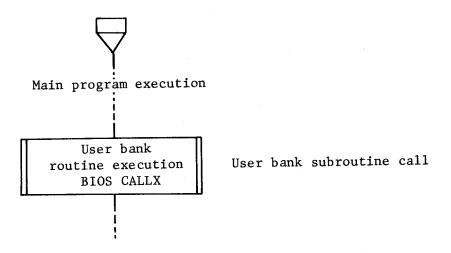

User bank 1 can be used as a program area or data area as long as MFBASIC is not started. User bank 2 can be used in the same manner. When one of the user banks is to be used as program area, the program must be loaded into the corresponding bank. This is done as follows.

- (1) Read in one sector of the subroutine program by calling BDOS from a program in the main bank.

- (2) Call BIOS routine LDIRX to transfer the data read to user bank 1 or 2.

- (3) Repeat steps 1 and 2 until the entire subroutine has been loaded.

- (4) Start processing with the main program after subroutine program loading has been completed.

- (5) Use the CALLX routine of BIOS to call the subroutine in the user bank. (CALLX makes it possible to execute subroutines in other banks.)

These procedures are shown as a flowchart below.

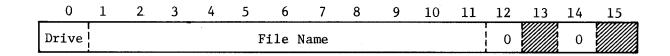

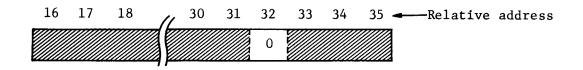

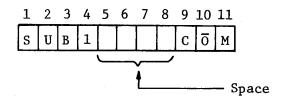

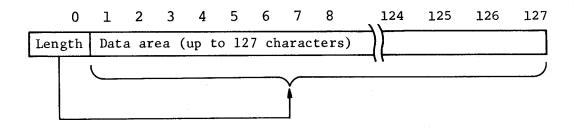

FCB for BDOS calls

As shown above, the FCB (file control block) is composed of 36 bytes. The FCB is referenced by BDOS when a file is accessed. Specification of a file control block is mandatory whenever the user accesses a program or data file on a flexible disk.

An example of the FCB specification for opening a subroutine program file is shown below.

Byte 0: Drive number

- 0 Disk currently logged in

- 1 Drive A

- 2 Drive B

- 3 Drive C

- 4 Drive D

Bytes 1 - 11: Filename

Example: SUB1.COM

Only upper-case characters can be specified for the file name.

Bytes 12, 14, and 32: Set to 0.

Any data may be specified for bytes which are shaded.

When a file is opened by making a BDOS call, prepare an FCB such as that shown above before making the call.

Normally the FCB is located in the main bank area starting at address 05CH. However, it can also be prepared in a user program area.

#### 2.2 Switching Banks

User programs are normally loaded into the main bank area from 0100F to 0DFFFH for execution. However, if memory banks are switched during program execution, program control is switched to the selected memory bank. Therefore, at the user's option it is possible to continue program execution in the selected bank. (See 2.1 "Using the User Banks" for procedures for loading programs or data into banks other than the main bank.) The sequence for switching memory banks is as follows.

- (1) Save the current bank number.

- (2) Set the new bank number in the BIOS common data area.

- (3) Output the new bank number to the applicable I/O port.

If the above sequence is loaded into part of resident memory, there will be no problem with execution of the next instruction even if banks are switched. Therefore, every effort should be made to avoid switching banks from other than resident memory, and BIOS entries LDIRX, JUMPX, or CALLX should be used for continuing execution.

An example of coding for continuation of a program in another bank is shown below.

| MEMBANK | EQU | ØFEFØH      | CURRENT BANK NO.      |

|---------|-----|-------------|-----------------------|

| CBANK   | EQU | 030H        | ;I/O FORT.            |

| NBANK   | EQU | 018H        | ;I/O PORT.            |

|         | ĎΙ  |             | ;DISABLE INTERRUPT.   |

|         | IN  | A, (CBANK)  | KEEP CURRENT BANK NO. |

|         | LD. | (SVBANK),A  | <b>5</b>              |

|         | LD  | A,040H      | ;SELECT USER BANK.    |

|         | LD  | (MEMBANK),A | ;SET NEW BANK NO.     |

|         | OUT | (NBANK),A   | ; CHANGE.             |

|         | ΕI  |             | ; ENABLE INTERRUPT.   |

|         |     |             |                       |

| SVBANK: | DS  | 1           | ;BANK NO. SAVE AREA.  |

In the example above, MEMBANK is the BIOS control data byte in the BIOS common data area which is used for saving the current bank number. Since BIOS uses this information for switching banks, the new bank number must be set in MEMBANK. The bank number is set as a bit pattern (see below) in which only one of the bits is set to "l". Note that operation is not assured if more than one bit of this bit pattern is "l". Also note that access to all memory other than the resident area (addresses 0E000H to 0FFFFH) will be cut off if all bits of this pattern are set to "0".

| Bank                     | Bit pattern |

|--------------------------|-------------|

| Main bank                | 010H        |

| System bank (BIOS)       | 020Н        |

| User bank 1              | 040H        |

| User bank 2 (option RAM) | 080н        |

#### §3 Keyboard Control

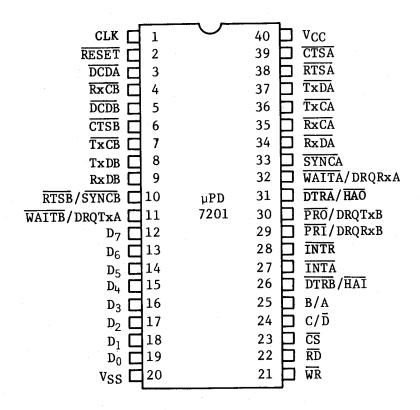

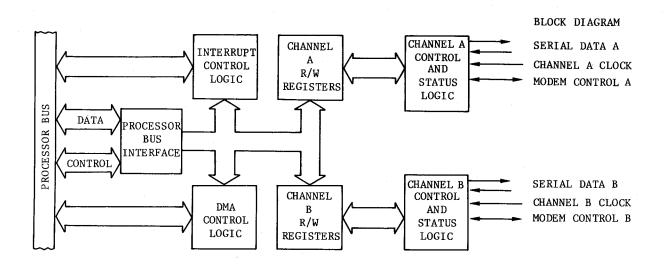

The keyboard is interfaced with the system via an NEC  $\mu$ PD7201. Data transfer between the keyboard and the main system is bidirectional, and is performed at 1200 bps. The signals used for transfer of data are as follows.

| Pin No. | Signal  |

|---------|---------|

| 1       | RxD     |

| 2       | Clock   |

| 3       | +12 VDC |

| 4       | TxD     |

| 5       | GND     |

| 6, 7, 8 | NC/GND  |

Data sent to the main system from the keyboard includes (1) the matrix codes of keys pressed, and (2) the LED status codes. The control and status codes for the LEDs are as shown in the table below.

LED control/status codes

| Key       | Control | code    | Status | code |

|-----------|---------|---------|--------|------|

|           | On      | Off     | On     | Off  |

| CAPS LOCK | 41H     | 40H     | ClH    | СОН  |

| INSert    | 45 H    | 44H     | С5Н    | С4Н  |

| SF4       | 49H     | 48H     | С9Н    | С8Н  |

| SF3       | SF3 4BH |         | СВН    | САН  |

| SF2       | 4 DH    | 4 CH    | CDH    | ССН  |

| SFl       | 4FH     | 4EH CFH |        | СЕН  |

Only matrix codes are generated when the keys are pressed; these matrix codes are converted into the corresponding internal character codes by the system software. The momentary shift keys (GRPH, left SHIFT, right SHIFT, and CTRL) generate both make and break codes. The keyboard matrix scanning codes generated are as shown in the following table.

### KEYBOARD SCAN CODES (ASCII)

|   | 0             | 1   | 2  | 3            | 4      | 5      | 6       | 7   | 8                    | 9 | Α | В | С                    | D . | Е | F |

|---|---------------|-----|----|--------------|--------|--------|---------|-----|----------------------|---|---|---|----------------------|-----|---|---|

| 0 |               |     |    |              |        |        |         |     |                      |   |   |   | CAPS<br>LOCKS<br>OFF |     |   |   |

| 1 | F4            | LF  |    | CAPS<br>LOCK |        | Q      | 2       | F3  |                      |   | · |   | CAPS<br>LOCK<br>ON   |     |   |   |

| 2 | F5            | A5  | Α4 | (SPACE)      |        | W      | #<br>3  | F2  |                      |   |   |   |                      |     |   |   |

| 3 | F6            |     |    | Z            | A      | E      | \$<br>4 | F1  |                      |   |   |   |                      |     |   |   |

| 4 | F7            | 000 |    | Х            | S      | R      | %<br>5  |     | SHIFT<br>(R)<br>BRK  |   |   |   | INS<br>OFF           |     |   |   |

| 5 | F8            |     | 3  | С            | D      | Т      | &<br>6  | ESC | SHIFT<br>(R)<br>MAKE |   |   |   | INS<br>ON            |     |   |   |

| 6 | F9            |     | 2  | v            | F      | Y      | ,<br>7  | :/  | SHIFT<br>(L)<br>BRK  |   |   |   | -                    |     |   |   |

| 7 | F10           | 0   | 1  | В            | G      | U      | (<br>8  | ТАВ | SHIFT<br>(L)<br>MAKE |   | 1 |   |                      |     |   |   |

| 8 | Al            | +   | _  | N            | Н      | I      | )<br>9  |     |                      |   |   |   | MF4<br>OFF           |     |   |   |

| 9 | BREAK         | 6   | 9  | М            | J      | 0      | 0       |     |                      |   |   | - | MF4<br>ON            |     |   |   |

| A | PAUSE         | 5   | 8  | <,           | K      | P      | =       |     | CTRL<br>BRK          |   |   |   | MF3<br>OFF           |     |   |   |

| В | S CAN<br>DUMP | 4   | 7  | >            | L      | @      | ~       |     | CTRL<br>MAKE         |   |   |   | MF3<br>ON            |     |   |   |

| С | HELP          |     | =  |              | +<br>; | {<br>[ |         |     | GRPH<br>BRK          |   |   |   | MF2<br>OFF           |     |   |   |

| D | A2            |     | *  |              | *      | }<br>] | BS      |     | GRPH<br>MAKE         |   |   |   | MF2<br>ON            |     |   |   |

| E | A3            |     | /  |              |        | INS    | НОМЕ    |     |                      |   |   |   | MF1<br>OFF           |     |   |   |

| F | SF1           |     | ,  |              | ? /    | DEL    | CLS     |     |                      |   |   |   | MF1<br>ON            |     |   |   |

**†**

Shift Key

1

LED

Data sent to the keyboard from the main system controls the keyboard as follows.

(1) Auto-repeat start time setting

The auto-repeat start time (the time from the moment a key is first pressed until the auto-repeat function starts operating) can be set in 25 ms increments within the range from 300 ms to 1075 ms.

(2) Auto-repeat interval setting

The auto-repeat interval (the interval at which input is accepted from a key after the repeat function starts operating) can be set to within the range from 30 ms to 185 ms in 5 ms increments.

(3) Auto-repeat control

The repeat function can be enabled or disabled. When disabled, only one character is input each time a key is pressed, no matter how long that key is held down.

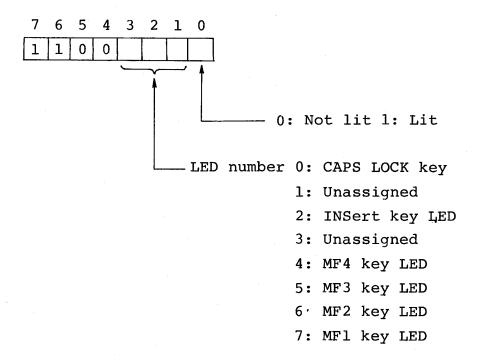

(4) Keyboard LED control

LEDs built into certain keytops can be turned on or off by specifying the corresponding LED number.

(5) LED status read

The current status of all LEDs (on or off) can be checked.

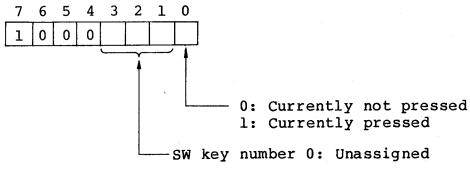

(6) SW status read

The current status of the keyboard switches (SHIFT, CTRL, and GRPH) can be checked.

(7) Keyboard enable/disable

Input from the keyboard buffer can be either enabled or disabled.

(8) Reset

The keyboard controller can be reset. The status upon reset is as follows.

- o The keyboard buffer (built into the keyboard) is cleared.

- o The repeat function is enabled.

- o The repeat starting time is set to 500 ms.

- o The repeat interval is set to 50 ms.

- o All LEDs are turned off.

The reset function also executes a keyboard diagnostic program which turns on the LEDs in sequence, then turns all LEDs on and back off again; and which scans all keys, outputting OH it no key is pressed and OFFH if any key is pressed.

Control commands for the eight functions described above

are summarized in the table below.

| Command                  |   | Bit pattern |     |          |     |                |     |                              | Example     |

|--------------------------|---|-------------|-----|----------|-----|----------------|-----|------------------------------|-------------|

|                          |   | 6           | 5   | 4        | 3   | 2              | 1   | 0                            | Вхатрте     |

| Repeat starting time set | 0 | 0           | 0   | *1       |     | nı             |     |                              | 00H ~ 01FH  |

| Repeat interval set      | 0 | 0           | 1   | *2       |     | n <sub>2</sub> |     |                              | 020н∿03ғн   |

| Repeat control           | 1 | 0           | 1   | X        | X   | х              | Х   | *3<br>ON/OFF                 | OAOH, OAlH  |

| LED ON/OFF               | 0 | 1           | 0   | х        | *4  | LED            | No. | *5<br>ON/OFF                 | 040H ∼ 04FH |

| LED status read          | 0 | 1           | 1   | l<br>I X | X   | Х              | X   | Х                            | 07FH        |

| SW status read           | 1 | 0           | . 0 | X        | X   | Х              | ! X | Х                            | 080н        |

| Keyboard enable          | 1 | 1           | ' 0 | X        | X   | Х              | Х   | *6<br>ON/OFF                 | OCOH, OC1H  |

| Reset                    | 1 | 1           | 1   | X        | ı X | Х              | х   | *7 <sub>Di-</sub><br>agnosis | OFEH        |

Either 0 or 1 may be specified for bits marked with an "x".

#### Notes:

- \*1,\*2 nl and n2 specify the repeat starting time and the repeat interval. The repeat starting time is equal to 300 ms + nl x 25 ms, and the repeat interval is equal to 30 ms + n2 x 5 ms.

- \*3 Bit 0 controls the repeat function. The repeat function is inhibited if 0 is set in bit 0, and is enabled if 1 is set in bit 0.

- \*4 With the LED status read command, bits 3, 2, and 1 designate the LED to be turned on or off as follows.

LED No.=0 - CAPS LOCK LED

LED No.=2 - INS LED

LED No.=4 - MF4 LED

LED No.=5 - MF3 LED

LED No.=6 - MF2 LED

LED No.=7 - MF1 LED

- \*5 This bit determines whether the specified LED is turned on or off. When bit 0 is 0, the LED is turned off; when it is 1, the LED is turned on.

- \*6 Input from the keyboard is inhibited if bit 0 is 0 (although data currently being sent is output); input is enabled if this bit is set to 1.

- \*7 Specifies execution of the diagnostic program. The diagnostic program is executed when bit 0 is set to 0, and is not executed when it is set to 1.

All of these keyboard control commands are output to I/O port 010H.

#### Example: Sequence to light the MF3 LED

```

.

LD A,01000111B; MF3 LED ON.

OUT (010H),A;

```

Normally, the results of the LED status read command or the SW status read command cannot be read by the BIOS CONIN routine. Therefore, the user must read in the value as follows.

(1) Call the BIOS CONST routine to confirm that there is no data in the keyboard buffer. If there is data and it can be ignored, initialize the keyboard data pointer as follows.

```

EQU

KBUF

ØFE2EH

KEYBOARD BUFFER ADDR.

INPTR

EQU

ØFE21H

; KEY PUT POINTER.

KEYPTR

EQU

ØFE23H

;KEY GET POINTER.

DI

; DISABLE INT.

LD

HL, KBUF

; INITIALIZE KEY DATA.

LD

(INPTR),HL

; POINTER.

(KEYPTR), HL ;

L.D

EI

```

- (2) Output the applicable command (LED or SW status read).

- (3) Call the CONST routine to wait until data is input.

- (4) Read in 8 bytes of data from KBUF (address OFE2EH) in the BIOS common data area for each command executed, then reinitialize the keyboard buffer.

The following is an example of a program which does steps 1 to 4 above.

```

KBUF

EQU

ØFE2EH

INTETR

EQU

ØFE21H

KEYPTR

EQU

ØFE23H

CONST

EQU

0F606H

CALL

CONST

; CHECK INPUT STATUS.

OR

CALL

NZ, KRINIT

; IF READY

LD

A,060H

; READ LED STATUS.

OUT

(010H),A

LD

HL.KBUF

KEY BUFFER HEAD ADDR.

B.8

LD

;8 TIMES.

LOOP:

PUSH

BC

PUSH

HL

CALL

CONST

; CHECK STATUS.

POP

HL

```

```

POP

BC

OR

Α

JR

Z, LOOP

; NO DATA.

LD

A, (HL)

: A=LED DATA.

INC

HL

DJNZ

LOOP

CALL

KBINIT

; INITIALIZE POINTER.

KBINIT:

DI

; SUBROUTINE.

LD

HL, KBUF

LD

(INTPTR), HL ; INITIALIZE KEY DATA.

(KEYPTR), HL ; POINTER.

LD

ΕI

RET

```

Eight bytes of data are returned as the result of the LED status read command. These values are composed of bit patterns such as the one shown below.

Example: The value 011001011B indicates that the MF3 key LED is lit.

Eight bytes are also returned as the result of the SW data read command. These are composed of bit patterns such as the following.

1: Unassigned

2: Right shift key

3: Left shift key

4: Unassigned

5: CTRL key

6: GRPH key

7: Unassigned

Example: The value 010000111B indicates that the left shift key is currently being pressed.

The repeat starting time, repeat interval, and repeat control can also be set by setting data in KBSTRT (address 0FE4DH), KBINTVL (address 0FE4EH), and KBREPT (address 0FE4CH) in the BIOS common data area. However, the values set are different in the case of repeat control; set 0FFH to enable the repeat function and 0H to disable it.

#### §4 Light Pen

Depending on the display mode with which it is used, light pen sensitivity may be quite low. This is particularly true when used with other than a green monitor in the non-MFBASIC normal mode. The reason for this is as follows.

Light pen detection by the  $\mu PD7220$  is performed by reading data twice and ignoring it if the results of the two reads do not match. For modes other than the non-MFBASIC normal mode (or other than a green monitor), there are 400 character addresses in the vertical direction; i.e., data addresses differ in 1-dot units. Therefore, if the light pen slips even slightly when it is pressed against the screen, the address (and particularly the vertical address) is likely to change. This means that the light pen must be held at a constant angle to the screen and kept from slipping in any direction. Further, sensitivity is particularly low with red when a color monitor is used.

This problem does not occur when the light pen is used with a green monitor in the non-MFBASIC normal mode.

The address detected by the light pen is posted by reading it in from an I/O port; however, the address read is not the same as the actual address of the screen area against which the light pen was pressed. BIOS corrects for this difference as follows.

|                                                       | Gree                       | en monitor                          | Color monitor                                                  |

|-------------------------------------------------------|----------------------------|-------------------------------------|----------------------------------------------------------------|

| Display mode                                          | Non-MFBASIC<br>Normal mode | Non-MFBASIC MF<br>mode/MFBASIC mode | Non-MFBASIC normal<br>mode/Non-MFBASIC MF<br>mode/MFBASIC mode |

| Correction value<br>(2 bytes)                         | -5 (OFFFBH)                | -2 (OFFFEH)                         | -3 (OFFFDH)                                                    |

| BIOS common data area containing the correction value | MLPBIAS<br>(OFEF6H)        | GLPBIAS<br>(OFE9BH)                 | CLPBIAS<br>(OFEF4H)                                            |

As indicated above, different 2-byte correction values are stored in the BIOS common data area for each mode. If the address read differs from the actual one by too much, these values can be changed using the DDT transient command. See the discussion of CONOUT in Chapter 1 for procedures for using DDT to change data in the BIOS common data area.

#### §5 RS-232C Interface

Including the optional RS-232C cards, the QX-10 supports a total of 5 RS-232C interface channels. Except with respect to maximum transfer speed, processing for both the standard and optional interfaces is performed in exactly the same manner. Further, data can be received on all five channels simultaneously as long as the following conditions are satisfied.

- (a) The transfer speed must not be more than 300 bps.

- (b) SI/SO control must not be used.

- (c) XON/XOFF control may be specified; however, in this case the interfaces cannot be used for transfer of binary data.

- (d) Every effort should be made to minimize I/O access and bank switching during processing of receive data. It is particularly important to avoid access to flexible disk drives or output of data to the screen.

BIOS routines provided for using the RS-232C interfaces include RSOPEN, RSCLOSE, RSINST, RSOUTST, RSIN, RSOUT, and RSIOX. However, except for RSIOX, these routines can only be used for control of the main board interface. Therefore, the RSIOX routine must be called for control of the optional RS-232C interfaces. Further, the receive buffer is fixed to the 512-byte area starting at address ODAOOH of the system bank for all routines other than RSIOX. This means that the RSIOX routine cannot be used together with other RS-232C control routines.

The standard RS-232C interface can be assigned to any logical device name (LST:, PUN:, RDR:, or CON:) by specifying the appropriate setting in the I/O byte. Assignment of the RS-232C interface to a logical device does not open the interface; the interface is opened only when data is input or output. The RS-232C interface is opened by resetting it (the  $\mu$ PD7201). Therefore, the standard RS-232C interface cannot be used by a user program or MFBASIC when it has been specified in the I/O byte. In this case, use one of the optional RS-232C interfaces for standard system I/O.

When connecting an HX-20 to the QX-10 via their RS-232C interfaces, data sent from the HX-20 to the QX-10 will be shifted by one bit (resulting in an error) if the RS-232C interface on the QX-10 side is opened before that on the HX-20 side. The reason for this is that when the HX-20's RS-232C interface is opened, noise is output during initialization of the interface when its power is turned on. The QX-10 interprets this noise as a start bit, so that subsequent data received is shifted by one bit. Therefore, be sure to open the RS-232C interface of the HX-20 prior to that of the QX-10.

All RS-232C interfaces are set to the asynchronous mode by BIOS. When any of the interfaces is to be used in the synchronous mode, jumper settings must be changed and RS-232C control must be provided.

The jumper settings for the respective modes are as follows.

Main board RS-232C interface

| Mode<br>Jumper | Asynchronous <b>&lt;</b> | ⇒Synchronous |

|----------------|--------------------------|--------------|

|                | Al                       | В1           |

| J2             | A2                       | В2           |

Changing these settings for synchronous communication causes the external clock to be used in the case of the main board RS-232C interface.

Jumper settings for the optional RS-232C interface cards are as follows.

| Mode   | <b>+</b>     | Synchronous            |                        |  |  |  |

|--------|--------------|------------------------|------------------------|--|--|--|

| Jumper | Asynchronous | External<br>Send Clock | Internal<br>Send Clock |  |  |  |

| J6     | В            | A                      | В                      |  |  |  |

| J7     | Α            | В                      | В                      |  |  |  |

When the interfaces are set to the synchronous mode, the external clock is used as the receive clock.

Settings of the various registers for synchronous communication are described below.

#### PIN CONFIGURATION

#### PIN DESCRIPTION

#### μPD**720**1

| ***   | P                              | IN                                                          | PHOODIDMICAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|--------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.   | SYMBOL                         | NAME                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12-19 | D <sub>0</sub> -D <sub>7</sub> | System Data Bus<br>(bidirectional,<br>3-state)              | The system data bus transfers data and commands between the processor and the ${\tt IPD7201.}\  \   D_0$ is the least significant bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 25    | B/Ā                            | Channel A or B Select<br>(input, High selects<br>Channel B) | This input defines which channel is accessed during a data transfer between the processor and the µPD7201.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24    | c/D                            | Control or Data Select<br>(input, High selects<br>Control)  | This input defines the type of information transfer performed between the processor and the $\mu PD7201$ . A High at this input during a processor write to or read from the $\mu PD7201$ causes the information on the data bus to be interpreted as a command for the channel selected by $B/A$ . A low at $C/D$ means that the information on the data bus is data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23    | CS                             | Chip Select (input, active Low)                             | A low level at this input enables the $\mu PD7201$ to accept command or data inputs from the processor during a write cycle, or to transmit (data to the processor during a read cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1     | CLK                            | System Clock (input)                                        | The µPD7201 uses standard TTL clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 22    | RD                             | Read (input active Low)                                     | If $\overline{RD}$ is active, a memory or I/O read operation is in progress. $\overline{RD}$ is used with $C/\overline{D}$ . $B/\overline{A}$ and $\overline{CS}$ to transfer data from the $\mu PD7201$ to the processor or the memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 21    | WR                             | Write (input, active Low)                                   | The $\overline{WR}$ signal is used to control the transfer of either command or data from the processor or the memory to the µPD7201.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2     | RESET                          | Reset (input, active Low)                                   | A low RESET disables both receivers and transmitters, forces TxDA and TxDB marking, forces the modem controls high and disables all interrupts. The control registers must be rewritten after the µPD7201 is reset and before data is transmitted or received. RESET must be active for a minimum of one complete CLK cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10,38 | RTSA, RTSB                     | Request to Send (outputs, active Low)                       | When the RTS bit is set, the RTS output goes Low. When the RTS bit is reset in the Asynchronous mode, the output goes High after the transmitter is empty. In Synchronous modes, the RTS pin strictly follows the state of the RTS bit. Both pins can be used as general-purpose outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10,33 | SYNCA, SYNCB                   | Synchronization (inputs/outpus, active Low)                 | These pins can act either as inputs of outputs. In the Asynchronous Receive mode, they are inputs similar to CTS and DCD. In this mode, the transitions on these lines affect the state of the Sync/Hunt status bits in Read Register O. In the External Sync mode, these lines also act as inputs. When external synchronization is achieved. SYNC must be driven Low on the second rising edge of RXC after that rising edge of RXC on which the last bit of the sync character was received. In other words, after the sync pattern is detected, the external logic must wait for two full Receive Clock cycles to activate the SYNC input. Once SYNC is forced Low, it is wise to keep it Low until the processor informs the external sync logic that synchronization has been lost or a new message is about to start. Character assembly begins on the rising edge of RXC that immediatley precedes the falling edge of SYNC in the External Sync mode. |

|       |                                |                                                             | In the Internal Synchronization mode (monosync and Bisync), these pins act as outputs that are active during the part of the receive clock (RxC) cycle in which sync characters are recognized. The sync condition is not latched, so these outputs are active each time a sync pattern is recognized, regardless of character boundaries.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 26,31 |                                |                                                             | These outputs follow the state programmed into the DTR bit. They can also be programmed as general-purpose outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# PIN DESCRIPTION (CONT.)

μPD7201

|                | PIN                              |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|----------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.            | SYMBOL                           | NAME                                                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27             | INTA                             | Interrupt<br>Acknowledge (input,<br>active Low)        | This signal is generated by the processor and is sent to all peripheral devices. It serves to acknowledge the interrupt and to allow the highest priority interrupting device to put an 8-bit vector on the bus. INT and INTA are compatible with the fully nested option of the uPD8259A-5.                                                                                                                                                               |

| 29             | PRI                              | Priority In (input, active Low)                        | These signals are daisy chained through the peripheral device controllers. The signal on these lines is intact until a device with a pending interrupt request is found on the chain. After that device, this signal holds off lower priority device interrupts. A higher                                                                                                                                                                                  |

| 30             | PRO                              | Priority Out (output, active Low)                      | priority device can interrupt the processing of an interrupt from a lower priority device, provided the processor has interrupts enabled.                                                                                                                                                                                                                                                                                                                  |

|                |                                  |                                                        | PRI is used with PRO to form a priority daisy chain when there is more than one interrupt-driven device. A low on this line indicates that no other device of higher priority is being serviced by a processor interrupt service routine.                                                                                                                                                                                                                  |

|                |                                  |                                                        | PRO is Low only if PRI is Low and the processor is not servicing an interrupt from the µPD7201. Thus, this signal blocks lower priority devices from interrupting while a higher priority device is being serviced by its processor interrupt service routine.                                                                                                                                                                                             |

| 11,29<br>30,32 | DRQTxA, DRQTxB<br>DRQRxA, DRQRxB | DMA Request<br>(outputs, active High)                  | These signals are generated by the receiver or transmitter of Channel A and Channel B. These signals can be connected to most DMA Controllers directly and are used for handshaking during DMA transfer.                                                                                                                                                                                                                                                   |

| 26             | IAH                              | DMA Acknowledge<br>(input, active Low)                 | Typically, the HLDA signal driven from the processor is input to the HAI terminal of the highest priority µPD7201, and the HAO output of that µPD7201 is daisy chained to the HAI input of the lower priority                                                                                                                                                                                                                                              |

| 31             | HAO                              | DMA Acknowledge<br>(output, active Low)                | μPD7201 and propagated downstream. HAI and HAO signals provide aknowledgement for the highest priority outstanding DMA request.                                                                                                                                                                                                                                                                                                                            |

| 28             | INT                              | Interrupt Request (output, open collector, active Low) | When the $\mu PD7201$ is requesting an interrupt, it pulls $\overline{\mbox{INT}}$ low.                                                                                                                                                                                                                                                                                                                                                                    |

| 11,32          | WAITA, WAITB                     | (Outputs, open drain)                                  | Wait lines for both channels that synchronize the processor to the $\nu PD7201$ data rate. The reset state is open drain.                                                                                                                                                                                                                                                                                                                                  |

| 6,39           | CTSA, CTSB                       | Clear to Send<br>(inputs, active Low)                  | When programmed as Auto Enables, a Low on these inputs enables the respective transmitter. If not programmed as Auto Enables, these inputs may be programmed as general-purpose inputs. Both inputs are Schmitt-trigger buffered to accommodate slow-risetime inputs. The µPD7201 detects pulses on these inputs and interrupts the processor on both logic level transitions. The Schmitt-trigger inputs do not guarantee a specified noise-level margin. |

| 3,5            | DCDA, DCDB                       | Data Carrier Detect<br>(inputs, active Low)            | These signals are similar to the CTS inputs, except they can be used as receiver enables.                                                                                                                                                                                                                                                                                                                                                                  |

| 9,34           | RxDA, RxDB                       | Receive Data (inputs, active High)                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8,37           | TxDA, TxDB                       | Transmit Data (outputs, active High)                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.35           | RxCA, RxCB                       | Receiver Clocks<br>(inputs)                            | The Receiver Clocks may be 1, 16, 32, or 64 times the data rate in asynchronous modes. Receive data is sampled on the rising edge of RxC.                                                                                                                                                                                                                                                                                                                  |

| 7,36           | TxCA, TxCB                       | Transmitter Clocks<br>(inputs)                         | In asynchronous modes, the Transmitter Clocks may be 1, 16, 32, or 64 times the data rate. The multiplier for the transmitter and the receiver must be the same. Both TxC and RxC inputs are Schmitt-trigger buffered for relaxed rise- and fall-time requirements (no noise margin is specified). TxD changes on the falling edge of TxC. Note that TxC and RxC in Channel B are on a common pin, RxCB/TxCB.                                              |

#### **BLOCK DIAGRAM**

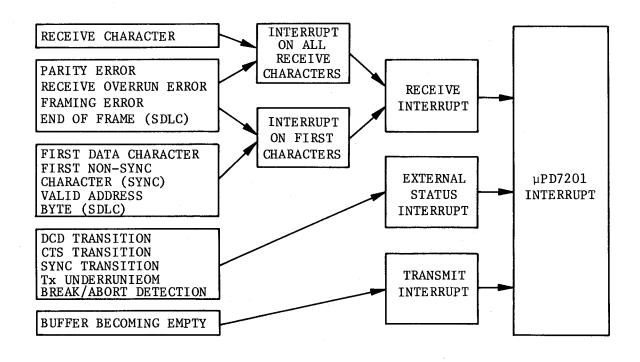

#### INTERRUPT STRUCTURE

| WRO | 7        | 6        | 5         | 4           | 3           | 2        | 1.         | 0     |

|-----|----------|----------|-----------|-------------|-------------|----------|------------|-------|

|     | CRC1     | CRC0     | CMD2      | CMD1        | CMD0        | PTR2     | PTRl       | PTRO  |

|     | 00 Null  |          | 000 Null  |             |             | (000 WRO | ,RRO)      |       |

|     | 01 Reset | Rx CRC   | 001 Send  | Abort (SDL  | C)          | 001 WR1  | ,RR1       |       |

|     | Chec     | ker      | 010 Reset | E/S INT     |             | 010 WR2  | ,RR2 (CH.B | only) |

|     | 10 Reset | Tx CRC   | 011 Chann | el Reset    |             | 011 WR3  |            |       |

|     | Gene     | rator    | 100 Enabl | e INT on N  | ext Rx CHAR | 100 WR4  |            |       |

|     | 11 Resét | Tx       | 101 Reset | Tx INT/DM   | A Pending   | 101 WR5  |            |       |

|     | Unde     | rrun/EOM | 110 Error | Reset       |             | 110 WR6  |            |       |

|     | Bit      |          | lll End c | of INT (CH. | A only)     | 111 WR7  |            |       |

| R1 | 7         | 6 | 5       | 4         | 3             | 2               | 1          | 0         |

|----|-----------|---|---------|-----------|---------------|-----------------|------------|-----------|

|    | Wait      | 0 | Wait on | Rx INT    | Rx INT        | Status          | Tx INT/DMA | E/S INT   |

|    | Enable    |   | Rx/Tx   | Mode 1    | Mode 0        | Affects         | Enable     | Enable    |

|    |           |   | :       |           |               | Vector          |            |           |

|    | 0 Disable | 0 | 0 Tx    | 00 INT/DN | MA Disable    | 0 Fixed         | 0 Disable  | 0 Disable |

|    | l Enable  |   | l Rx    | 01 INT or | n First CHAR. | Vector          | l Eable    | l Enable  |

|    |           |   |         |           | n All CHAR.   | l Modi-<br>fied |            |           |

|    |           | 1 |         | . (=      |               | Vector          |            |           |

|    |           |   |         | 11 INT or | n All CHAR.   |                 |            |           |

|    |           |   |         | (Parit    | ty included)  |                 |            |           |

| WR2A | 7              | 6   | 5        | 4        | 3          | 2 *       | 1         | 0       |

|------|----------------|-----|----------|----------|------------|-----------|-----------|---------|

|      | RTSB/SYNC3     | . 0 | Vector   | INT      | INT        | Priority  | INT/DMA   | INT/DMA |

|      | Select Mode    |     | Mode     | Model    | Mode 0     | Select    | Model     | Mode 0  |

|      | 0 RTSB 0 0 Nor |     | 0 Non-   | 00 35-3  | l Vectored | 0 TxA-RxB | 00 Both C | CH. INT |

|      | 1 SYNC3        |     | Vectored | 01 35-2  | 2 Vectored | l RxB-TxA | 01 CH.A:D | MA      |

|      | 1 Vectored     |     | 10 36    | Vectored |            | CH.B:I    | NT        |         |

|      |                |     |          |          |            | 10 Both C | CH.DMA    |         |

<sup>\* 0:</sup> RxA TxA RxB TxB E/SA E/SB 1: RxA RxB TxA TxB E/SA E/SB

High ----- Low

| WR2B | . 7            | 6  | 5              | 4  | 3              | 2              | 1              | 0                |

|------|----------------|----|----------------|----|----------------|----------------|----------------|------------------|

|      | V <sub>7</sub> | ٧4 | V <sub>5</sub> | V4 | V <sub>3</sub> | V <sub>2</sub> | V <sub>1</sub> | . V <sub>0</sub> |

| WR3   | 7              | 6     | 5         | 4               | 3.        | 2      | 1         | 0         |

|-------|----------------|-------|-----------|-----------------|-----------|--------|-----------|-----------|

|       | Rx Rx          |       | Auto      | Enter           | Rx        | Adrs   | CYNC CHAR | Rx        |

| į     | Bits/          | Bits/ | Enable    | Hunt            | CRC       | Search | Load      | Enable    |

|       | CHAR1          | CHAR0 |           | Phase           | Enable    | Mode   | Inhibit   |           |

| Async | 00 5Bits/CHAR. |       | 0 Disable | 0               | 0         | 0      | 0         | 0 Disable |

|       | 01 7Bits/CHAR. |       | l Enable  | ·               | U         | U      | 0         | l Enable  |

| Sync  | 10 6Bits/CHAR. |       |           | 0 Nop           | 0 Disable |        | 0 Nop     | 1 Midple  |

| _     | ll 8Bits/CHAR. |       |           | l Re-<br>enable | l Enable  |        | l Inhibit |           |

| WR4      | 7         | 6        | 5         | 4      | 3                                    | 2                       | 1        | 0         |

|----------|-----------|----------|-----------|--------|--------------------------------------|-------------------------|----------|-----------|

|          | Clock     | Clock    | SYNC      | SYNC   | Stop                                 | Stop                    | Parity   | Parity    |

|          | Rate 1    | Rate 0   | Mode 1    | Mode 0 | Bits 1                               | Bits 0                  | Even/Odd | Enable    |

|          | 00 xl Cl  | ock Mode |           |        | 01 1 stop                            | bit/CHAR                | 0 Odd    | 0 Disable |

| Async    | 01 x16 C1 | ock Mode |           | 00     | 10 1 <sup>1</sup> / <sub>2</sub> sto | 10 1 1/2 stop bits/CHAR |          | l Enable  |

| 2        | 10 x32 Cl | ock Mode |           |        | 11 2 stop                            | bits/CHAR               |          |           |

|          | 11 x64 C1 | ock Mode |           |        |                                      |                         |          |           |

|          |           |          | 00 8 bit  | SYNC   | 00 SYNC M                            | ode                     |          |           |

| Sync     |           | 00       | 01 16 bit | SYNC   |                                      |                         |          |           |

| <u> </u> | - v .     |          | 11 EXT SY | NC     |                                      |                         |          |           |

| WR5   | 7       | 6         | 5             | 4         | 3         | 2         | 1          | 0         |

|-------|---------|-----------|---------------|-----------|-----------|-----------|------------|-----------|

|       | DTR     | Tx Bits/  | Tx Bits/      | Send      | Тx        | CRC-16/   | RTS        | Tx CRC    |

|       |         | CHAR 1    | CHAR 0        | Break     | Enable    | CCITT     |            | Enable    |

|       | 0 DTR=1 | 00 5 or L | ess Bits/CHAR | 0 Marking | 0 Disable | 0         | 0 RTS=1    | 0         |

| Async | 1 DTR=0 | 01 7 Bits | /CHAR.        | 1 Spacing | l Enable  |           | (all sent) |           |

|       |         | 10 6 Bits | /CHAR.        |           |           |           | 1 RTS=0    |           |

| Sync  |         | ll 8 Bits | /CHAR.        |           |           | 0 CCITT-0 | 0 RTS=1    | 0 Disable |

|       |         |           |               |           |           | 1 CRC-16  | 1 RTS=0    | l Enable  |

|          |     |                      |     | V    | IR7  |    |   |     |               |      |     | W     | R6   |     |   |   |

|----------|-----|----------------------|-----|------|------|----|---|-----|---------------|------|-----|-------|------|-----|---|---|

|          | 7   | 6                    | 5   | 4    | 3    | 2  | 1 | 0   | 7             | 6    | 5   | 4     | 3    | 2   | 1 | 0 |

| - 100    |     |                      | SYN | C Bi | t 15 | ∿8 |   |     |               | *    | SYN | C Bi  | t 7º | v 0 |   |   |

| Async    | not | t used               |     |      |      |    |   |     | not used      |      |     |       |      |     |   |   |

| Monosync | Rx  | x SYNC CHAR.         |     |      |      |    |   |     | Tx STNC CHAR. |      |     |       |      |     |   |   |

| Bisync   | SYN | YNC CHAR. Bit 15 ∿ 8 |     |      |      |    |   | SYN | С СН.         | AR.  | Bit | 7 ∿ 0 |      |     |   |   |

| EXT sync | not | not used             |     |      |      |    |   |     | Тх            | SYNC | CHA | R.    |      |     |   |   |

| RR0      | 7        | 6         | 5       | 4        | 3       | 2         | 1        | 0         |

|----------|----------|-----------|---------|----------|---------|-----------|----------|-----------|

|          | Break/   | Tx Under- | CTS     | SYNC/    | DCD     | Tx Buffer | INT      | Rx CHAR.  |

|          | Abort    | run/EOM   |         | Hunt     |         | Empty     | Pending  | Available |

|          | l Break  | Unknown   | 1 CTS=0 | 1 SYNC=0 | 1 DCD=0 | l Tx Buff | l INT    | 1 Rx CHAR |

| Async    | Detected |           | 0 CTS=1 | 0 SYNC=1 | 0 DCD=1 | Empty     | Pending  | Available |

| 1        | 0 Normal |           |         |          |         | 0 Tx Buff | 0 No INT | 0 Rx Buff |

|          | L        |           |         |          |         | Full      | Pending  | Empty     |

| EXT sync |          | 1 Tx      |         |          |         | 1 Tx Buff | (CH.A    |           |

|          | 0        | Underrun  |         |          |         | Empty     | only)    |           |

| Monosync |          | /EOM      | 1       | l Hunt   |         | 0 Tx Buff |          |           |

| Bisync   |          | 0 Not Tx  |         | Phase    |         | Full      |          |           |

|          |          | Underrun  |         | 0 Exit   |         | (With or  |          |           |

|          |          |           |         | Hunt     |         | without   |          |           |

|          |          |           |         | Phase    |         | CRC)      | ı        |           |

|          |          | L         | l       |          |         |           | L        |           |

| RR1   | 7               | 6                        | 5                      | 4                 | 3                 | 2                 | 1                 | 0                   |

|-------|-----------------|--------------------------|------------------------|-------------------|-------------------|-------------------|-------------------|---------------------|

|       | End of<br>Frame | CRC/<br>Framing<br>Error | Rx<br>Overrun<br>Error | Parity<br>Error   | Residue<br>Code 2 | Residue<br>Code l | Residue<br>Code O | All Sent            |

| Async |                 | l Framing<br>Error       | l Rx<br>Overrun        | l Parity<br>Error | Unknown           |                   |                   | l All Sent<br>O Not |

|       | 0               | 0 No Error               | Error<br>0 No Error    | 0 No Error        |                   |                   |                   | All Sent            |

| Sync  |                 | Error<br>0 No Error      |                        |                   |                   |                   |                   | 1                   |

| RR2                   | 7              | 6              | - 5            | 4              | 3         | 2              | 1              | 0              |

|-----------------------|----------------|----------------|----------------|----------------|-----------|----------------|----------------|----------------|

| WR1 D2=0              | V <sub>7</sub> | V <sub>6</sub> | V <sub>5</sub> | V <sub>4</sub> | V 3       | V <sub>2</sub> | V <sub>1</sub> | V <sub>0</sub> |

| WR1 D <sub>2</sub> =1 |                |                |                | 1 CH. A        | 00 Tx Buf | fer Empty      |                |                |

|                       |                |                |                | 0 СН. В        | 01 Extern | al/Status      |                |                |

|                       |                |                |                |                |           | Change         |                |                |

| WR2A D                | V7             | V <sub>6</sub> | V <sub>5</sub> |                | 10 Receiv | e Character    | V <sub>1</sub> | V <sub>0</sub> |

| D =00,01              |                |                |                |                |           | Available      |                |                |

|                       |                |                |                |                | ll Specia | 1 Rx           |                |                |

|                       |                |                |                |                |           | Condition      |                |                |

#### Note:

Register WR0 can be set directly, but other registers (WR1 to WR7) are set by setting the register number in WR0 and then setting the data. Further, RR0 can be read directly from the I/O port, but PR1 can only be read after its register number has been written into WR0.

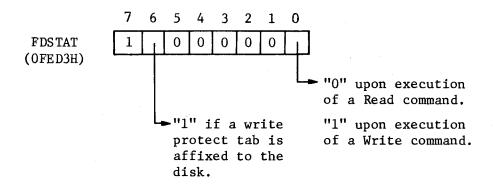

## §6 Flexible Disks

# 6.1 Flexible disk layout

|           | tor<br>0 1      | 6              | 32             | 48 60 6                               |

|-----------|-----------------|----------------|----------------|---------------------------------------|

| ack<br>00 | Boot Loader     | ССР            | вроз           | · · · · · · · · · · · · · · · · · · · |

| .01       | OS (main bank)  |                |                |                                       |

| 02        |                 | I<br>BIOS ( sy | stem bank )    |                                       |

| 03        |                 |                |                |                                       |

| 04        | Directory & FCB | File block 1   | File block 2   | File block 3                          |

| 05        | File block 4    | File block 5   | File block 6   | File block 7                          |

|           |                 |                |                |                                       |

|           |                 |                |                |                                       |

| 38        | File block 136  | File block 137 | File block 138 | File block 139                        |

| 39        |                 | Unuse          | ed area        |                                       |

| Track | Sector | Page # | Memory address<br>when loaded<br>in QX-10 | CP/M Module name |

|-------|--------|--------|-------------------------------------------|------------------|

|       | _      |        |                                           | _                |

| 00    | 00,01  |        | 0F000Н                                    | Boot Loader      |

|       | 02,03  |        | 0F100H                                    |                  |

|       | 04,05  |        | 0F200H                                    |                  |

| ļ     | 06,07  |        | 0F300H                                    |                  |

|       | 08,09  | -      | 0F400H                                    |                  |

|       | 10,11  |        | 0F500н                                    |                  |

|       | 12,13  |        | 0F600н                                    |                  |

|       | 14,15  |        | 0F700H                                    |                  |

| 00    | 16,17  | 00     | 0Е000Н                                    | CCP              |

|       | 18,19  | 01     | 0Е100Н                                    |                  |

|       | 20,21  | 02     | 0Е200Н                                    |                  |

|       | 22,23  | 03     | 0Е300Н                                    |                  |

|       | 24,25  | 04     | 0Е400Н                                    |                  |

|       | 26,27  | 05     | 0Е500Н                                    |                  |

|       | 28,29  | 06     | 0Е600Н                                    |                  |

|       | 30,31  | 07     | 0Е700Н                                    |                  |

| 00    | 32,33  | 08     | 0Е800Н                                    | BDOS             |

|       | 34,35  | 09     | 0Е900Н                                    | ·                |

|       | 36,37  |        | ОЕАООН                                    |                  |

|       | 38,39  | 11     | 0ЕВ00Н                                    |                  |

|       | 40,41  | 12     | ОЕСООН                                    |                  |

|       | 42,43  | 13     | OEDOOH                                    |                  |

|       | 44,45  |        | OEEOOH                                    | ·                |

|       | 46,47  | 15     | ОЕГООН                                    |                  |

|       | 48,49  | 16     | 0F000н                                    |                  |

|       | 50,51  | 17     | 0F100H                                    |                  |

|       | 52,53  | 18     | 0F200H                                    |                  |

|       | 54,55  | , 19   | 0F300H                                    |                  |

|       | 56,57  | 20     | OF400H                                    |                  |

|       | 58,59  | 21     | 0F500H                                    |                  |

|    | r              |    |        |                    |

|----|----------------|----|--------|--------------------|

| 00 | 60,61          | 22 | 0F600н | BIOS (main bank)   |

|    | 62,63          | 23 | 0F700H |                    |

| 01 | 00,01          | 24 | 0F800н |                    |

|    | 02,03          | 25 | 0F900Н |                    |

|    | 04,05          | 26 | OFA00H |                    |

|    | 06,07          | 27 | 0FB00H |                    |

|    | 08,09          | 28 | 0FС00Н |                    |

|    | 10,11          | 29 | OFDOOH |                    |

|    | 12,13          | 30 | OFEOOH |                    |

|    | 14,15          | 31 | OFFOOH |                    |

| 01 | 16,17          | 32 | ОН     | BIOS (system bank) |

|    | 18,19          | 33 | 100н   |                    |

|    | 20,21          | 34 | 200н   |                    |

|    | 22,23          | 35 | 300н   |                    |

|    | 24,25          | 36 | 400н   |                    |