# Introduction to The Instructor 50 Desktop Computer

Introduction to

The Instructor 50

Desktop Computer

by

J. E. Doll

Signetics reserves the right to make changes in the products contained in this book in order to improve design or performance and to supply the best possible products. Signetics also assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representations that the circuits are free from patent infringement. Applications for any integrated circuits contained in this publication are for illustration purposes only and Signetics makes no representation or warranty that such applications will be suitable for the use specified without further testing or modification. Reproduction of any portion hereof without the prior written consent of Signetics is prohibited.

© 1978 Signetics Corporation

#### **PREFACE**

Computers today are a pervasive part of our society. No longer the exclusive domain of large corporations, computers are now available to nearly everyone at a price comparable to good stereo equipment. Specialized computers are already being used in home appliances, video games, and automobiles.

This manual is written especially for people just starting to explore the world of computers. It is designed to give you background information, an understanding of how computers work, and insights into their functions.

As you read the manual, you will be introduced to a lot of new terminology. You are urged to pay particluar attention to these new terms, called "buzz words," as they are defined. Each buzz word embodies a basic concept of computer or electronic technology. They will be underlined in the text as they appear. Through an understanding of these concepts, you will become familiar with your Instructor 50 or any other microcomputer. If you are not sure you understand a term or concept, it is wise to review its definition or explanation before you proceed.

Armed with your new knowledge you will be able to apply your Instructor 50 to a variety of functions. This variety is limited only by your own imagination. As a stand-alone unit, the Instructor 50 can be used as a home message center, a digital clock, a stop watch, or a game center. By connecting it to other external devices it can be used to play music on your stereo, provide video games on your T.V., keep your household records, and compute your financial records.

So, welcome to the world of computers! You have nothing to fear.

Computers are no longer mysterious giants; they are as easy to operate as your automobile or microwave oven.

# **TABLE OF CONTENTS**

| PREFACE    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CHAPTER I  | INTRODUCTION AND BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|            | Historical Perspectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-1  |

|            | Concept of Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-2  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| CHAPTER II | THE BUILDING BLOCKS OF COMPUTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|            | Logic Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-1  |

|            | Combining Logic Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-2  |

|            | Flip/Flops: The Next Level of Complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-9  |

|            | Combining Flip/Flops into Counting Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-13 |

|            | Combining Flip/Flops into Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-16 |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| CHAPTER II | I HOW COMPUTERS COUNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| I.         | The Binary Numbering System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-1  |

| II.        | Conversion from Binary to Decimal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-5  |

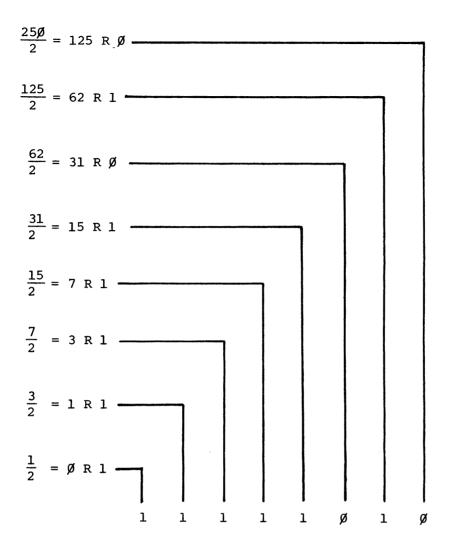

| III.       | Conversion from Decimal to Binary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-6  |

| IV.        | Binary Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-8  |

|            | Addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-8  |

|            | Subtraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-10 |

|            | Multiplication and Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-13 |

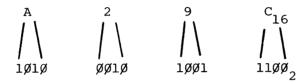

| V.         | The Hexadecimal Numbering System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|            | A Convenient Compromise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-14 |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| CHAPTER IV | INSIDE YOUR INSTRUCTOR 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

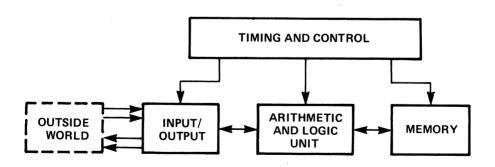

| I.         | Basic Computer Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-1  |

|            | Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-2  |

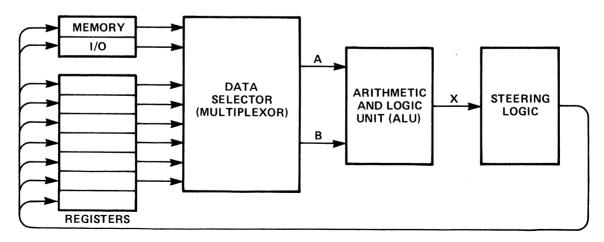

|            | The Arithmetic and Logic System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-4  |

|            | The Input/Output System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-6  |

|            | The Timing and Control System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-8  |

|            | Central Processor Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-9  |

| II.        | Computer Wares                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-9  |

|            | Title by the company of the company |      |

|           | Moving Information Between Blocks 4-1                | 0   |

|-----------|------------------------------------------------------|-----|

|           | Software vs. Firmware 4-1                            | 2   |

|           | Organization of the 2650 CPU 4-1                     | 3   |

|           | The Program Status Word 4-1                          | 6   |

| III.      | How It All Works Together 4-1                        | 7   |

|           | Instruction is Fetched 4-1                           | 7   |

|           | Instruction is Executed 4-1                          | 8   |

|           | Example: A One-Instruction Program 4-1               | 9   |

|           | Example: A Two-Instruction Program 4-2               | 1   |

| IV.       | Types of Instructions (What Instructions Can Do) 4-2 | 2   |

|           | Arithmetic Instructions 4-2                          | 3   |

|           | Input/Output (I/O) Instructions 4-2                  | :3  |

|           | Load and Store Instructions 4-2                      | 3   |

|           | Logical Instructions 4-2                             | :3  |

|           | Branch Instructions 4-2                              | :5  |

|           | Multi-Byte Instructions 4-2                          | :7  |

|           | Addressing Modes 4-2                                 | :9  |

| v.        | Interpreting Instruction Descriptions 4-3            | 5   |

|           | Making it Work 4-3                                   | 8   |

| CHAPTER V | PROGRAMMING TECHNIQUES                               |     |

| I.        | Organizing Your Program 5-1                          |     |

| II.       | Looping and Branching 5-9                            | )   |

| III.      | Subroutines                                          | .3  |

|           | Nested Subroutines 5-2                               | 20  |

| IV.       | Interrupts                                           | 2:2 |

|           | -                                                    | 7   |

GLOSSARY

# **LIST OF TABLES AND FIGURES**

#### FIGURES

| 1.1  | THE 2650 MICROPROCESSOR 1-2                         |

|------|-----------------------------------------------------|

| 1.2  | ABACUS                                              |

| 1.3  | FUNDAMENTAL COMPUTING TASK 1-4                      |

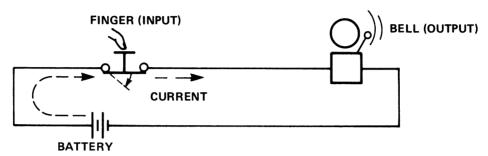

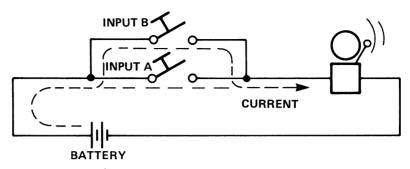

| 2.1  | DOORBELL CIRCUIT                                    |

| 2.2  | ALARM CIRCUIT                                       |

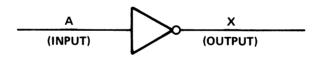

| 2.3  | LOGIC SYMBOL FOR INVERTER                           |

| 2.4  | TRUTH TABLE FOR INVERTER                            |

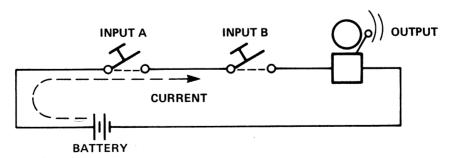

| 2.5  | AND CIRCUIT                                         |

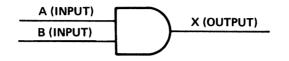

| 2.6  | LOGIC SYMBOL FOR AND GATE                           |

| 2.7  | TRUTH TABLE FOR AND GATE 2-5                        |

| 2.8  | OR CIRCUIT                                          |

| 2.9  | LOGIC SYMBOL FOR OR GATE 2-6                        |

| 2.10 | TRUTH TABLE FOR OR GATE                             |

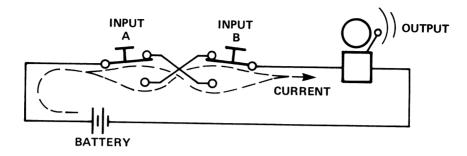

| 2.11 | EXCLUSIVE-OR CIRCUIT                                |

| 2.12 | LOGIC SYMBOL FOR EXCLUSIVE-OR GATE 2-7              |

| 2.13 | TRUTH TABLE FOR EXCLUSIVE-OR GATE                   |

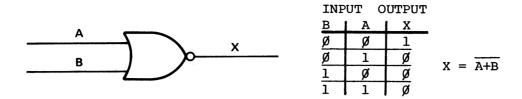

| 2.14 | LOGIC SYMBOL AND TRUTH TABLE FOR NAND GATE 2-8      |

| 2.15 | SYMBOL AND TRUTH TABLE FOR NOR GATE 2-9             |

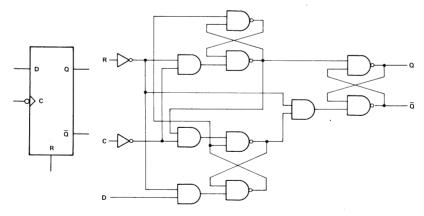

| 2.16 | LOGIC SYMBOL AND SCHEMATIC FOR D-TYPE FLIP/FLOP 2-9 |

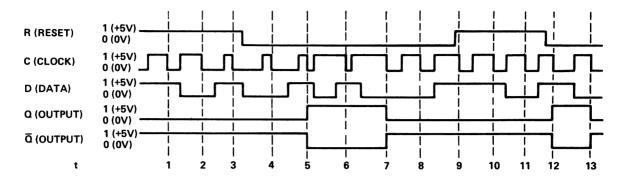

| 2.17 | FLIP/FLOP TIMING DIAGRAM 2-1                        |

| 2.18 | FLIP/FLOP TRUTH TABLE                               |

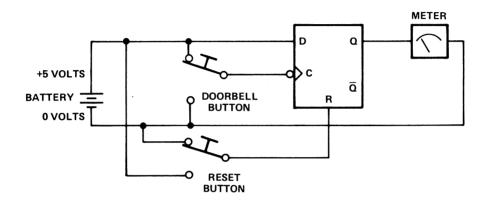

| 2.19 | DOORBELL MEMORY CIRCUIT                             |

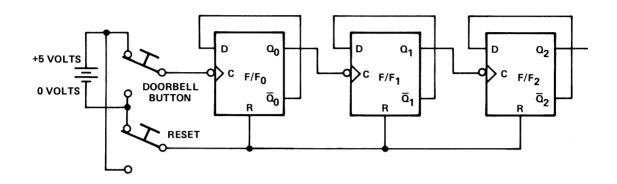

| 2.20 | DOORBELL COUNTING CIRCUIT                           |

| 2.21 | OUTPUT STATES OF DOORBELL COUNTING CIRCUIT 2-1      |

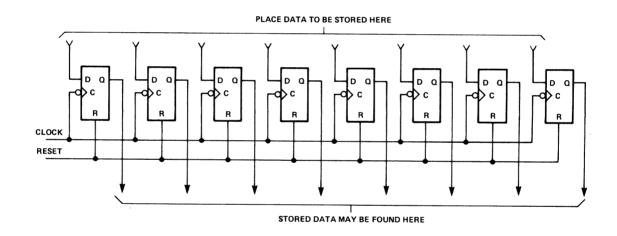

| 2.22 | AN 8-BIT REGISTER                                   |

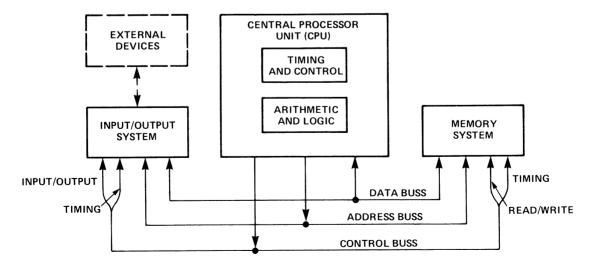

| 4.1  | BASIC COMPUTER ORGANIZATION                         |

| 4.2  | DIAGRAM OF 2650 MEMORY                              |

| 4.3  | ARITHMETIC AND LOGIC SYSTEM BLOCK DIAGRAM 4-4       |

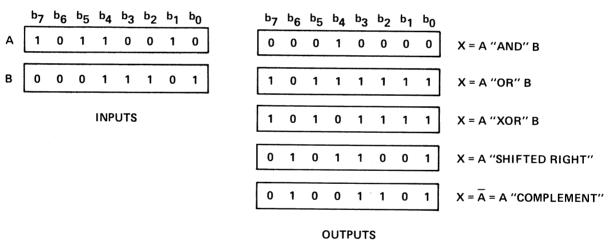

| 4.4  | ALU LOGICAL OPERATIONS                              |

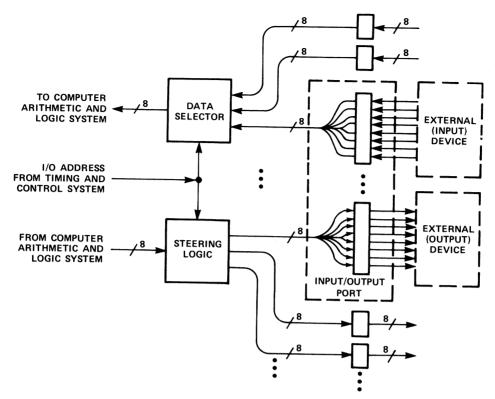

| 4.5  | INPUT/OUTPUT SYSTEM                                 |

| 4.6    | COMPUTER COMMUNICATIONS PATHS                       |

|--------|-----------------------------------------------------|

| 4.7    | 2650 CPU REGISTERS                                  |

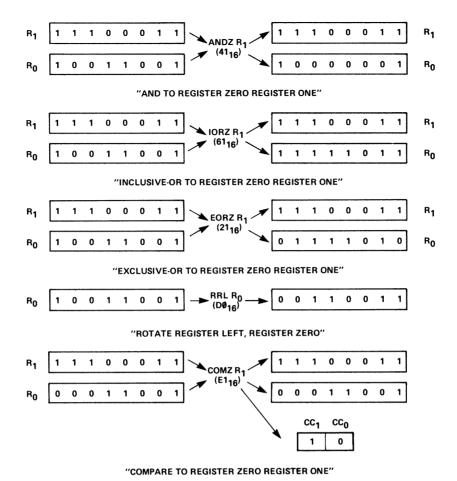

| 4.8    | EXAMPLES OF LOGICAL INSTRUCTIONS 4-24               |

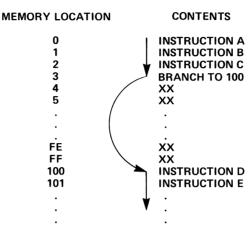

| 4.9    | OPERATION OF BRANCH INSTRUCTION 4-26                |

| 4.10   | OPERATION OF CONDITIONAL BRANCH INSTRUCTION 4-2     |

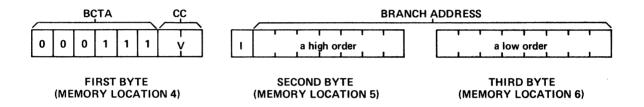

| 4.11   | FORMAT OF BCTA INSTRUCTION 4-28                     |

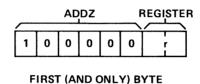

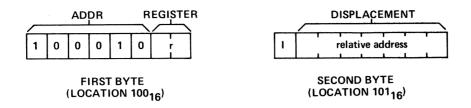

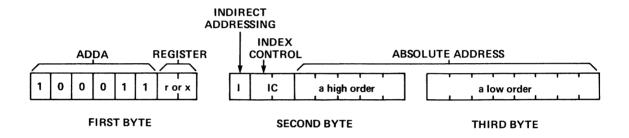

| 4.12   | FORMAT OF ADDZ INSTRUCTIONREGISTER ADDRESSING 4-30  |

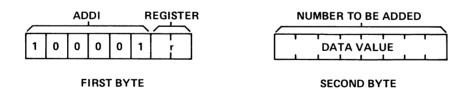

| 4.13   | FORMAT OF ADDI INSTRUCTIONIMMEDIATE ADDRESSING 4-30 |

| 4.14   | FORMAT OF ADDR INSTRUCTIONRELATIVE ADDRESSING 4-32  |

| 4.15   | FORMAT OF ADDA INSTRUCTIONABSOLUTE                  |

|        | ADDRESSING WITH INDEXING 4-3                        |

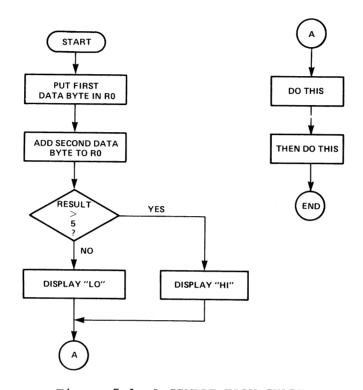

| 5.1    | A SIMPLE FLOW CHART 5-2                             |

| 5.2    | MNEMONIC LISTING ON CODING FORM 5-3                 |

| 5.3    | DEFINING LABELS 5-5                                 |

| 5.4    | CODING THE INSTRUCTIONS 5-7                         |

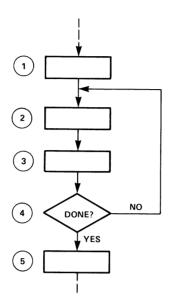

| 5.5    | A CONDITIONAL LOOP                                  |

| 5.6    | FLOWCHART TO FLASH LIGHT 5-10                       |

| 5.7    | A ONE SECOND TIME DELAY 5-1:                        |

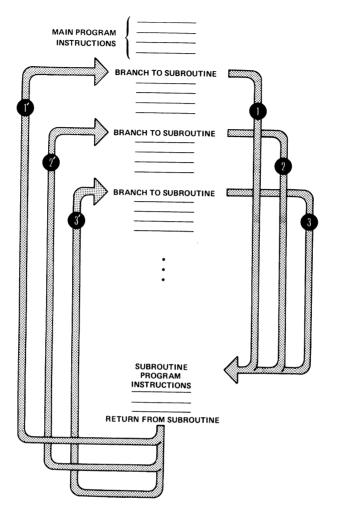

| 5.8    | PROGRAM WITH SUBROUTINE 5-1                         |

| 5.9    | TIME DELAY SUBROUTINE 5-1                           |

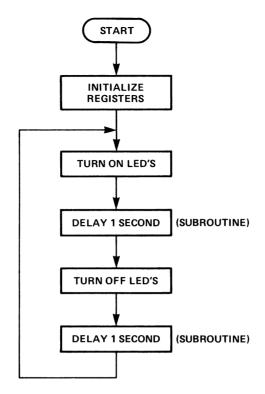

| 5.10   | FLOW CHART TO FLASH LED'S 5-18                      |

| 5.11   | PROGRAM TO FLASH LED'S                              |

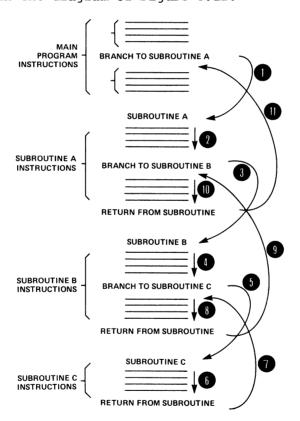

| 5.12   | NESTED SUBROUTINES 5-20                             |

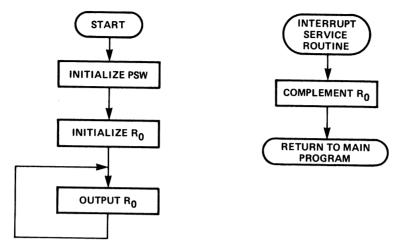

| 5.13   | PROGRAM USING INTERRUPT 5-2                         |

| 5.14   | CODE FOR PROGRAM USING INTERRUPT 5-24               |

| 5.15   | CODE FOR PROGRAM USING INDIRECT INTERRUPT 5-20      |

|        |                                                     |

|        |                                                     |

| TABLES |                                                     |

|        |                                                     |

| 3.1    | FLIP/FLOP COUNTING PATTERN                          |

| 3.2    | DECIMAL AND BINARY EQUIVALENTS                      |

| 3.3    | BINARY EQUIVALENTS OF POWERS OF 2                   |

#### 1. INTRODUCTION AND BACKGROUND

#### **Historical Perspectives**

In the early 1950s the very first commercial computers began to appear on the scene. At that time a computer was built of vacuum tubes, filled a one-story building, and required a specialized staff to maintain and operate it. It cost between half a million and a million dollars, and those were 1950 dollars. Market researchers for large corporations analyzed the new device and most of them concluded that due to its high cost of production and maintenance that perhaps 50 to 200 computers could be built and sold. After that they predicted the market would be flooded.

In spite of advice to the contrary, several corporations, notably IBM Corporation, added the computer to their product line. By the late 1950s and early 1960s many large corporations were using computers for their data processing operations. What is astounding is not the shortsightedness of the market researchers, but the technological advances which have occurred within the computer industry in the past few decades. With the invention of transistors, computers could be built for a small fraction of the size and cost of their vacuum tube counterparts. Soon it was discovered that thousands of transistors could be integrated onto a single tiny chip of silicon semiconducting material. Again, with the advent of these integrated circuits, the size, power, and cost requirements for a computer decreased dramatically. Funding provided for space program research during the 1960s provided a strong impetus for many of these technological breakthroughs. And as the size and cost of computer power was decreasing it became possible to produce more and more powerful computers, with more sophisticated functions. The 2650 microprocessor, the integrated circuit at the heart of your Instructor 50, provides more

sophisticated computational power than early commercial computers of the 1950s.

Figure 1.1 THE 2650 MICROPROCESSOR

While the size and cost of computing power was diminishing, sophistication available in commercial machines was increasing. But the basic principles of construction have remained essentially the same. These principles are used in virtually all computers being produced today, and are the basis for your Instructor 50. It is these principles which this manual will introduce and explain.

#### **Concept of Computer**

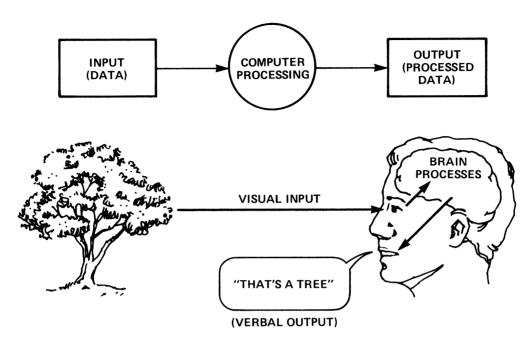

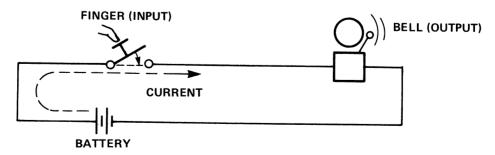

One of the earliest computing devices was the abacus. An abacus is an arrangement of beads which are slid along rods to form different patterns. Various positions of the beads represent different numbers. By manipulating the beads the operator of the abacus can perform mathematical problems quickly and accurately. Modern day digital computers are descendents of the abacus. The word <u>digital</u> is often associated with modern computers, implying that they operate using digits or numerical values. In reality, of course, what is manipulated is not numerical

values but electronic signals. We simply assign numerical value to the signals that are being manipulated just as the operator of the abacus assigns numerical value to the position of his beads.

Figure 1.2 ABACUS

With the computer, however, the process of sequentially manipulating the beads (substitute electronic signals) is automated. A human operator is not required. A computer, then, is a device for manipulating numbers. Unlike the abacus operator who can decide himself what problems to solve and how to solve them, the computer cannot make these decisions. These decisions are the job of the computer programmer.