# 17XXA-002

# Parallel Interface

# 17XXA-002

# Parallel Interface

P/N 717249

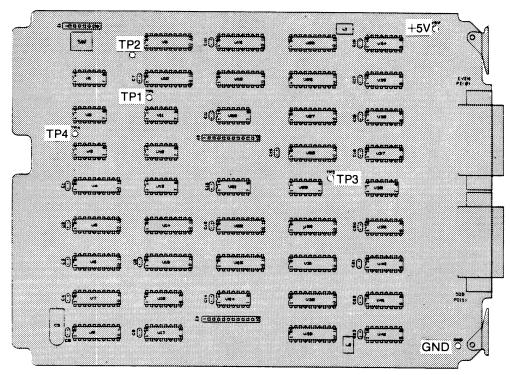

JUNE 1984

©1984 John Fluke Mfg. Co., Inc.

All rights reserved. Litho in U.S.A.

# WARRANTY

John Fluke Mfg. Co., Inc. (Fluke) warrants this instrument to be free from defects in material and workmanship under normal use and service for a period of one (1) year from date of shipment. Software is warranted to operate in accordance with its programmed instructions on appropriate Fluke instruments. It is not warranted to be error free. This warranty extends only to the original purchaser and shall not apply to fuses, computer media, batteries or any instrument which, in Fluke's sole opinion, has been subject to misuse, alteration, abuse or abnormal conditions of operation or handling.

Fluke's obligation under this warranty is limited to repair or replacement of an instrument which is returned to an authorized service center within the warranty period and is determined, upon examination by Fluke, to be defective. If Fluke determines that the defect or malfunction has been caused by misuse, alteration, abuse, or abnormal conditions of operation or handling, Fluke will repair the instrument and bill purchaser for the reasonable cost of repair. If the instrument is not covered by this warranty, Fluke will, if requested by purchaser, submit an estimate of the repair costs before work is started.

To obtain repair service under this warranty purchaser must forward the instrument, (transportation prepaid) and a description of the malfunction to the nearest Fluke Service Center. The instrument shall be repaired at the Service Center or at the factory, at Fluke's option, and returned to purchaser, transportation prepaid. The instrument should be shipped in the original packing carton or a rigid container padded with at least four inches of shock absorbing material. FLUKE ASSUMES NO RISK FOR INTRANSIT DAMAGE.

THE FOREGOING WARRANTY IS PURCHASER'S SOLE AND EXCLUSIVE REMEDY AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE OR USE. FLUKE SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OR LOSS WHETHER IN CONTRACT, TORT, OR OTHERWISE.

# **CLAIMS**

Immediately upon arrival, purchaser shall check the packing container against the enclosed packing list and shall, within thirty (30) days of arrival, give Fluke notice of shortages or any nonconformity with the terms of the order. If purchaser fails to give notice, the delivery shall be deemed to conform with the terms of the order.

The purchaser assumes all risk of loss or damage to instruments upon delivery by Fluke to the carrier. If an instrument is damaged in-transit, PURCHASER MUST FILE ALL CLAIMS FOR DAMAGE WITH THE CARRIER to obtain compensation. Upon request by purchaser, Fluke will submit an estimate of the cost to repair shipment damage.

Fluke will be happy to answer all questions to enhance the use of this instrument. Please address your requests or correspondence to: JOHN FLUKE MFG. CO., INC., P.O. BOX C9090, EVERETT, WA 98206, ATTN: Sales Dept. For European Customers: Fluke (Holland) B.V., P.O. Box 5053, 5004 EB, Tilburg, The Netherlands.

# **Contents**

| 1 | HOW TO USE THIS MANUAL                                                                                                                                                            | 1-1                                    |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   | Introduction                                                                                                                                                                      | 1-2<br>1-3<br>1-4<br>1-4<br>1-4        |

| 2 | INSTALLATION                                                                                                                                                                      | 2-1                                    |

|   | Introduction Unpacking And Shipping Information Installation Configuration Procedure Software Compatibility Installation Procedure Getting Started                                | 2-3<br>2-4<br>2-5<br>2-7<br>2-9        |

| 3 | INTERFACE DESCRIPTION                                                                                                                                                             | 3-1                                    |

|   | Introduction Hardware Interface Description Port Lines Port Signals Port Control Jumpers Notes on the Port Control Lines Port Direction Line (PDIR) Port Output Enable Line (POE) | 3-3<br>3-3<br>3-3<br>3-6<br>3-8<br>3-8 |

# **CONTENTS**, continued

|   | Interface Circuits Typical Receiver Circuit Typical Transmitter Circuits Transceiver for Bidirectional Data Transfer Handshake Modes Handshake Configuration Examples Introduction to the Handshake Timing Diagrams Mode 0 - No Handshake Mode 1 - Handshake Input Using Mode 1 to Strobe Data into the Port Peripheral Device Strobing Too Rapidly Mode 2 - Handshake Output Mode 3 - Strobe Output Handshake Using Mode 3 for Partial Handshake Operation | 3-15<br>3-17<br>3-19<br>3-21<br>3-23<br>3-24<br>3-25<br>3-27<br>3-29     |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|   | Some Notes On Using The Parallel Interface Board                                                                                                                                                                                                                                                                                                                                                                                                            | 3-31<br>3-31<br>3-32<br>3-33                                             |

| 4 | PARALLEL INTERFACE BOARD LIBRARY (PIBLIB.OBJ)                                                                                                                                                                                                                                                                                                                                                                                                               | 4-1                                                                      |

|   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3<br>4-4                                                               |

|   | Example 1. Converting A binary Digit to an integer                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                          |

|   | (Direction Mask) Example 2. Converting an Integer to a Binary Number .                                                                                                                                                                                                                                                                                                                                                                                      | 4-6<br>4-7                                                               |

|   | (Direction Mask) Example 2. Converting an Integer to a Binary Number . Event Interrupts                                                                                                                                                                                                                                                                                                                                                                     | 4-7<br>4-8                                                               |

|   | (Direction Mask) Example 2. Converting an Integer to a Binary Number .                                                                                                                                                                                                                                                                                                                                                                                      | 4-7                                                                      |

|   | (Direction Mask)  Example 2. Converting an Integer to a Binary Number.  Event Interrupts  Program Examples  Subroutine Reference Pages  CHKBIT                                                                                                                                                                                                                                                                                                              | 4-7<br>4-8<br>4-8<br>4-9<br>4-9                                          |

|   | (Direction Mask)  Example 2. Converting an Integer to a Binary Number  Event Interrupts  Program Examples  Subroutine Reference Pages  CHKBIT  CLRBIT                                                                                                                                                                                                                                                                                                       | 4-7<br>4-8<br>4-8<br>4-9<br>4-9<br>4-11                                  |

|   | (Direction Mask)  Example 2. Converting an Integer to a Binary Number.  Event Interrupts  Program Examples  Subroutine Reference Pages  CHKBIT  CLRBIT  SETBIT                                                                                                                                                                                                                                                                                              | 4-7<br>4-8<br>4-8<br>4-9<br>4-9<br>4-11<br>4-13                          |

|   | (Direction Mask)  Example 2. Converting an Integer to a Binary Number.  Event Interrupts  Program Examples  Subroutine Reference Pages  CHKBIT  CLRBIT  SETBIT  RDWRD                                                                                                                                                                                                                                                                                       | 4-7<br>4-8<br>4-8<br>4-9<br>4-11<br>4-13<br>4-15                         |

|   | (Direction Mask)  Example 2. Converting an Integer to a Binary Number.  Event Interrupts  Program Examples  Subroutine Reference Pages  CHKBIT  CLRBIT  SETBIT                                                                                                                                                                                                                                                                                              | 4-7<br>4-8<br>4-8<br>4-9<br>4-9<br>4-11<br>4-13                          |

|   | (Direction Mask) Example 2. Converting an Integer to a Binary Number Event Interrupts Program Examples Subroutine Reference Pages CHKBIT CLRBIT SETBIT RDWRD WTWRD RDBLK WTBLK                                                                                                                                                                                                                                                                              | 4-7<br>4-8<br>4-8<br>4-9<br>4-11<br>4-13<br>4-15<br>4-17<br>4-19         |

|   | (Direction Mask) Example 2. Converting an Integer to a Binary Number Event Interrupts Program Examples Subroutine Reference Pages CHKBIT CLRBIT SETBIT RDWRD WTWRD RDBLK WTBLK FRDBLK                                                                                                                                                                                                                                                                       | 4-7<br>4-8<br>4-8<br>4-9<br>4-11<br>4-13<br>4-15<br>4-17<br>4-21<br>4-23 |

|   | (Direction Mask) Example 2. Converting an Integer to a Binary Number Event Interrupts Program Examples Subroutine Reference Pages CHKBIT CLRBIT SETBIT RDWRD WTWRD RDBLK WTBLK                                                                                                                                                                                                                                                                              | 4-7<br>4-8<br>4-8<br>4-9<br>4-11<br>4-13<br>4-15<br>4-17<br>4-19         |

|      | PCLOSE                                                 |       |

|------|--------------------------------------------------------|-------|

|      | Error Messages                                         | 4-30  |

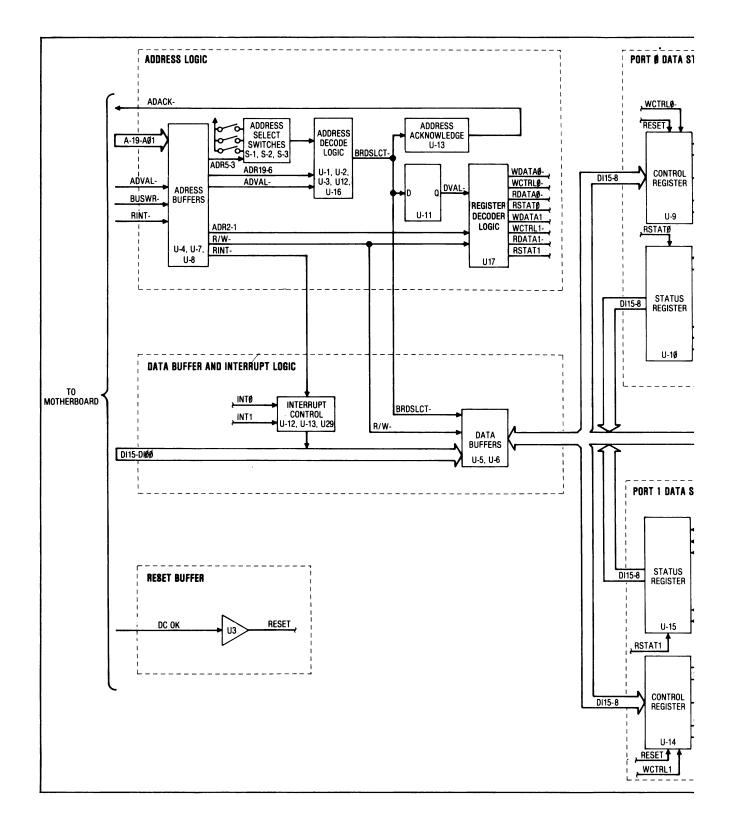

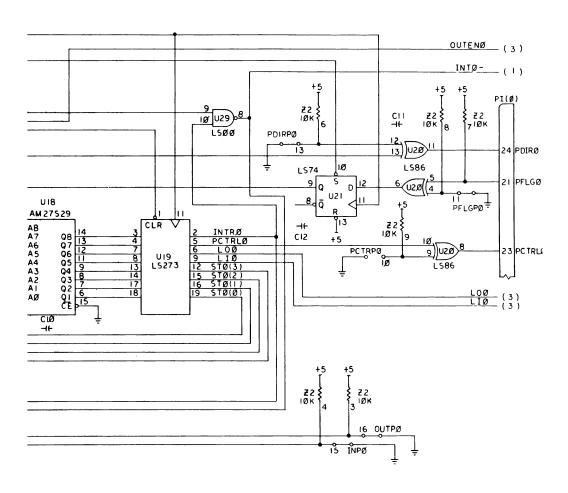

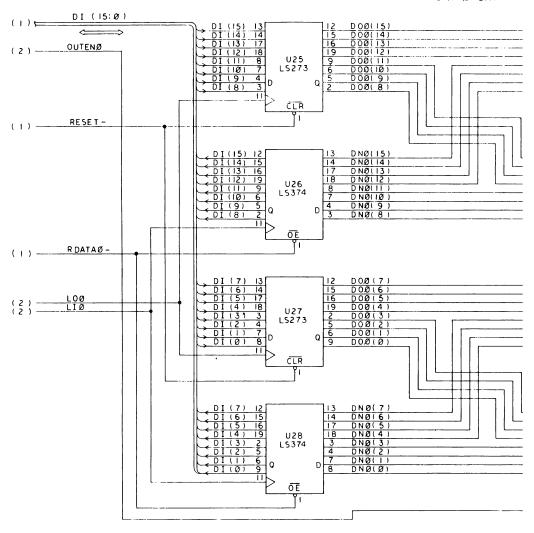

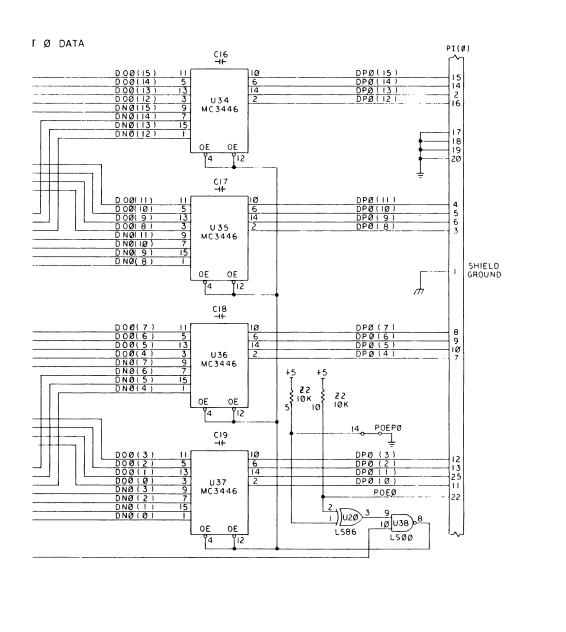

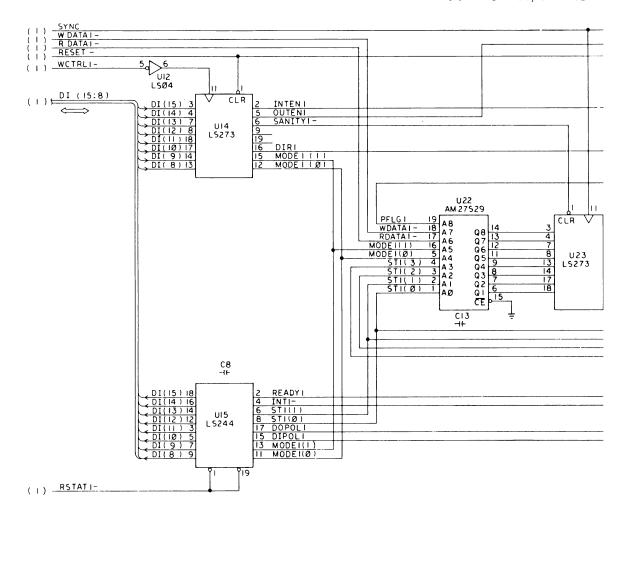

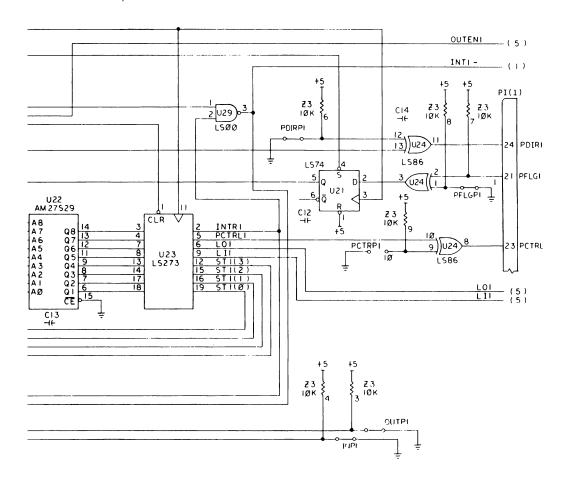

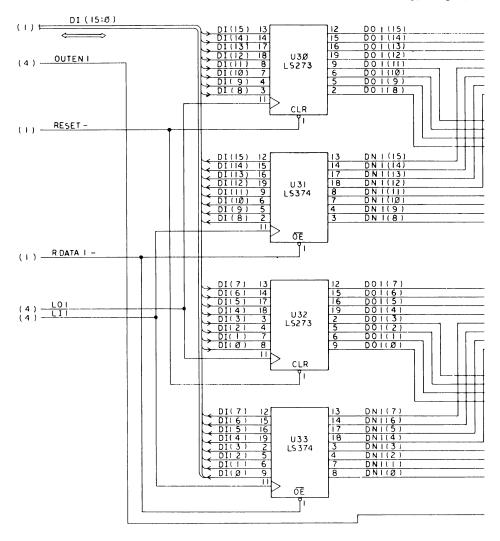

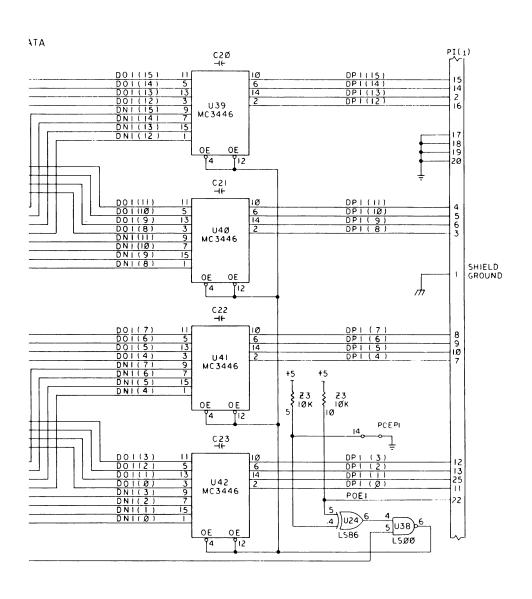

| 5    | THEORY OF OPERATION                                    | 5-1   |

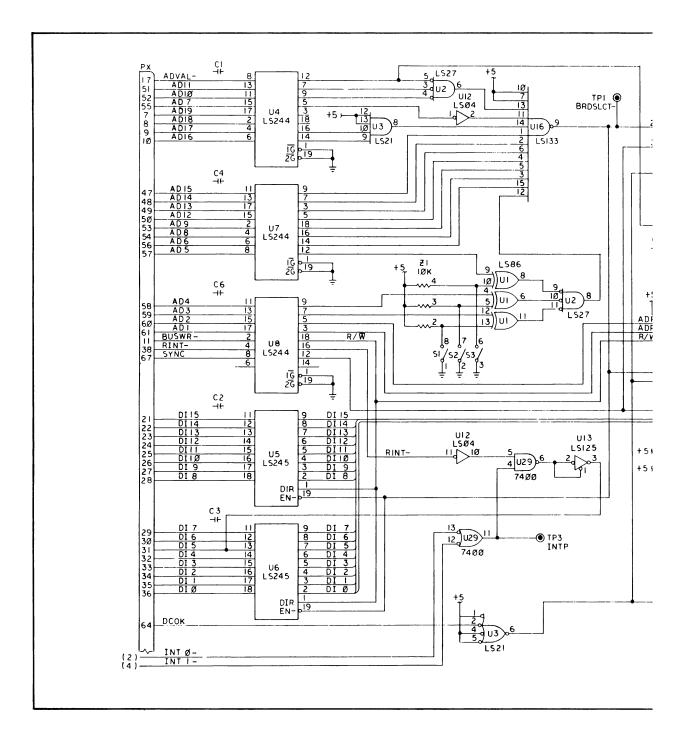

|      | Introduction                                           | 5-3   |

|      | Address Logic                                          | 5-3   |

|      | Address Buffers                                        | 5-3   |

|      | Address Switches and Decode Logic                      | 5-3   |

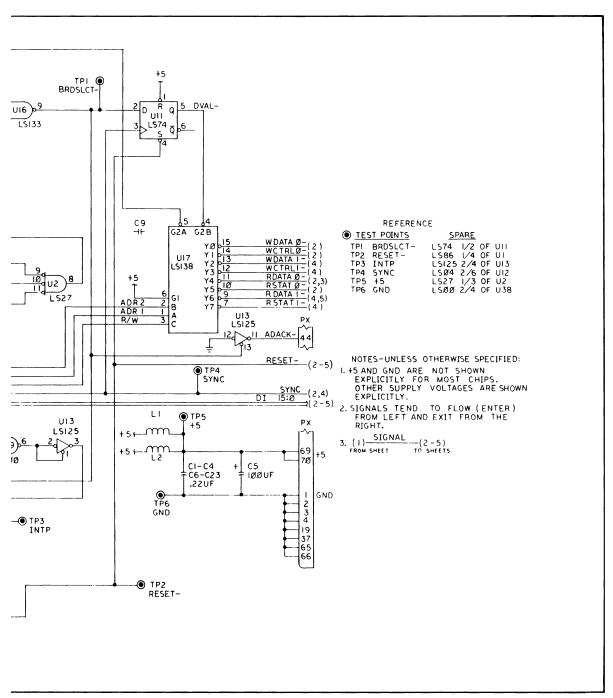

|      | Address Acknowledge Logic                              | 5-4   |

|      | Data Valid Flip-Flop                                   |       |

|      | Register Decoder                                       | 5-4   |

|      | Data Buffer and Interrupt Logic                        | 5-4   |

|      | Reset Buffer                                           |       |

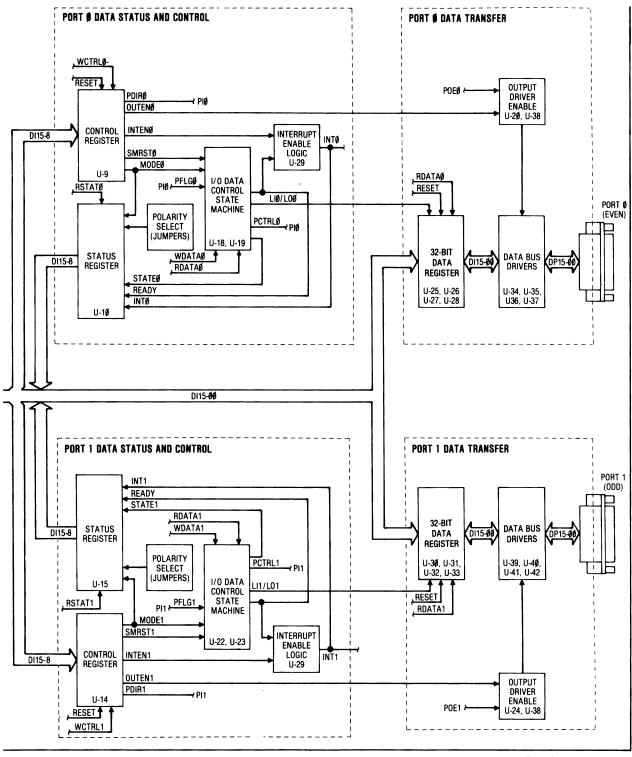

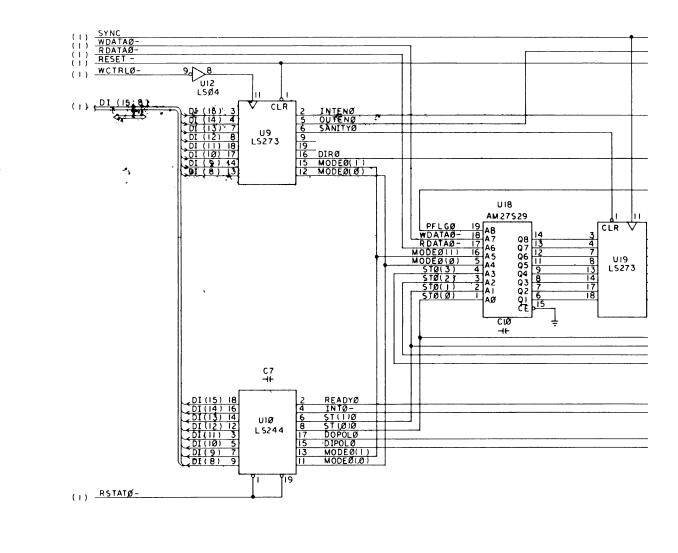

|      | Data, Status, and Control                              | 5-5   |

|      | Control Register                                       | 5-5   |

|      | Status Register                                        |       |

|      | Configuration Jumpers                                  | . 5-7 |

|      | State Machine                                          | . 5-7 |

|      | Interrupt Enable Logic                                 |       |

|      | Data Transfer Port                                     | . 5-7 |

|      | Output Driver Enable                                   | . 5-7 |

|      | 32-Bit Data Register                                   | . 5-8 |

|      | Data Bus Drivers                                       | . 5-8 |

| APPI | NDICES                                                 |       |

|      | A Specifications                                       | . A-1 |

|      | B Interface Connector Pinout                           |       |

|      | C Sample BASIC Programs                                |       |

|      | D Test Points                                          |       |

|      | E Signal Glossary                                      |       |

|      | F Using the Parallel Interface With a 1720A Instrument |       |

|      | Controller                                             |       |

|      | G Performance Testing                                  |       |

|      | H Schematics                                           | . H-l |

**INDEX**

Parallel Interface

# Section 1 How To Use This Manual

# **CONTENTS**

| Introduction                    | <br>1-2 |

|---------------------------------|---------|

| Organization                    | <br>1-3 |

| Usage Guide                     |         |

| Evaluators                      | <br>1-4 |

| Beginning Interface Designers   | <br>1-4 |

| Experienced Interface Designers |         |

| Troubleshooters                 |         |

#### INTRODUCTION

This manual is the primary reference for the Option 17XXA-002 Parallel Interface. The manual describes the hardware and software requirements for creating a customized parallel interface for Fluke Instrument Controllers.

The Parallel Interface manual provides a complete reference for effectively using the Parallel Interface Option. You do not need to be proficient in Assembly Language programming to program a parallel interface. Languages available are Interpreted BASIC, Compiled BASIC, FORTRAN, and TMS-99000 Assembly Language. You should be able to use timing diagrams; they illustrate the sequence of events required by hardware, and understanding them can assist you in using the software effectively.

#### ORGANIZATION

#### Section 1 How To Use This Manual

Describes the organization of the manual and how to use it.

#### Section 2 Installation

Describes how to install a parallel interface. This section contains unpacking instructions and general installation and setup procedures.

# Section 3 Interface Description

This section describes the interface as a hardware device controlled by software. It gives the signal names for each pin on the connector and briefly discusses the timing constraints of each signal. The four operating modes are presented with timing diagrams and a complete description of the conditions occurring during the entire handshake.

#### Section 4 PIBLIB Routines

This section discusses software control of the interface. It begins with a description of how to access the PIB library (PIBLIB) from the high-level languages and Assembly Language. Examples illustrate the steps needed to get the module performing an I/O function. This section describes in detail each of the routines in the library and presents the syntax for BASIC, FORTRAN, and Assembly Language programs.

# Section 5 Theory Of Operation

This section describes the architecture and hardware design of the Parallel Interface module. A block diagram serves as the focal point for a discussion of how the module works. Each functional circuit is briefly described.

## **Appendices**

The appendices contain useful reference material, including the specifications of the module, the connector pinout, test points, example programs, and a glossary of signal names.

#### Index

An index is provided to assist you in locating topical references.

#### **USAGE GUIDE**

This guide is intended to assist potential PIB (Parallel Interface Board) designers and users to evaluate this manual and the Parallel Interface option.

#### **Evaluators**

If your task is to evaluate the option for a particular application, refer to Appendix A, Specifications, for a summary of the hardware and software that make up the Fluke Parallel Interface option. You might also review Sections 3, 4, and 5 for a more detailed look at the option's capabilities.

## **Beginning Interface Designers**

If you have never designed a parallel interface, start with Section 2, Installation. That section contains preliminary setup instructions and shows the various configuration possibilities the PIB affords. Next, before going on to Sections 3 and 4, look over the contents of Appendix C, Sample Programs. These programs were all developed to meet real needs, and while they may have no direct applicability to your particular installation, they should serve as a source of ideas about how to proceed.

# **Experienced Interface Designers**

Those who have designed a programmable parallel interface in the past may not need to use the sample programs in Appendix C, but will want to proceed directly to Section 3 or 4 for a detailed look at the hardware and software that make up the option. However, Appendix A, Specifications, is recommended first because it is a concise reference to the hardware and software. Also, Section 2 will help with your preliminary setup.

#### **Troubleshooters**

Depending on the level of troubleshooting to be done, there are several ways to proceed:

- ☐ If there is uncertainty about whether the module or a program is causing a failure, the System Diagnostic Software disk includes a test program called PIBTST that can be used to verify the operation of the hardware. You might also use one of the sample loop programs in Appendix C to ensure the ability of each port to read and write data and to do handshaking.

- □ If the PIB seems to work with some programs, but not others, the hardware rather than the program may be at fault. In this case, the theory of operation discussion in Section 5 may be helpful. This information breaks the PIB into logical blocks, and may help uncover the reason a particular program is not working.

- ☐ If the PIB is known not to operate, more detailed servicing information and the schematic are presented in the 1722A Service Manual, which can be ordered as Fluke P/N 732156.

In any of these cases, Appendix C lists two short test programs that can verify both ports. The test programs use a loopback connector that connects to both ports and allows the program to send data out one port and back into the other. The test cable can be ordered from FLuke, or it can be constructed easily. Appendix C tells how to order or build a test cable.

The Parallel Interface Board is covered by the Module Exchange Program. Consult your local Fluke Service Center for full details.

# Section 2 Installation

# **CONTENTS**

| Introduction                       | 2-2 |

|------------------------------------|-----|

| Unpacking And Shipping Information | 2-3 |

| Installation                       |     |

| Configuration Procedure            |     |

| Software Compatibility             |     |

| Installation Procedure             |     |

| Getting Started                    |     |

# **INTRODUCTION**

This section describes how to unpack and install the Option 17XXA-002 Parallel Interface. The installation procedures include information about:

- □ Verifying the configuration switches and jumpers.

- □ Checking for software compatibility.

- □ Physically installing the module into the Controller.

The section ends with a few tips on how to get started in designing and programming the interface.

### UNPACKING AND SHIPPING INFORMATION

The Option 17XXA-002 Parallel Interface is packaged and shipped in a protective container. When you receive the option, make a thorough inspection for proper contents and possible shipping damage. Special instructions for inspection and claims are included with the shipping container. In the event the module must be shipped again later, use the original container. If the container is not available, a new one can be obtained from the John Fluke Mfg. Co., Inc. Please specify the instrument model number when requesting a new shipping container.

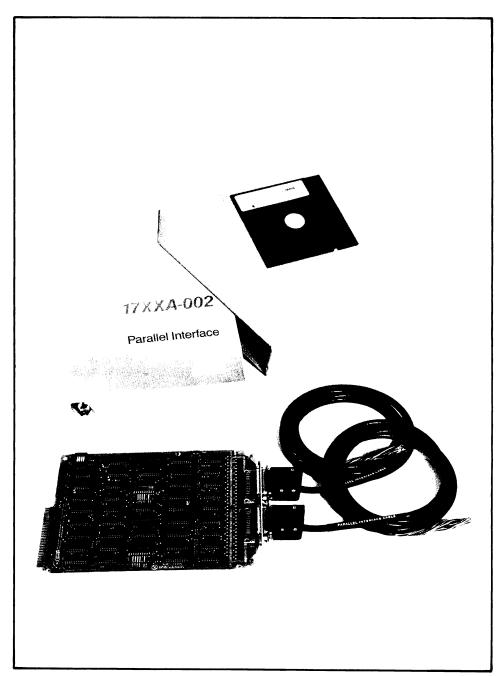

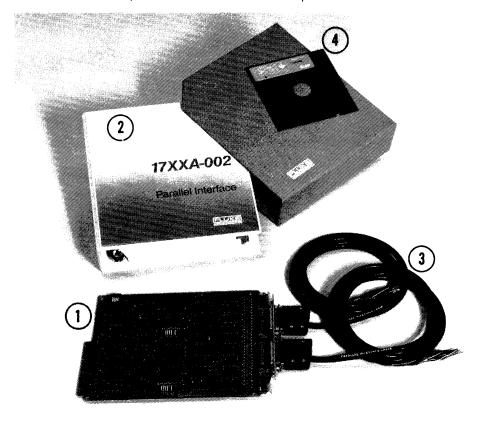

17XXA-002 Parallel Interface Option Contents

| ITEM                          | JOHN FLUKE PART NUMBER |

|-------------------------------|------------------------|

| Parallel Interface Module     | 611947                 |

| Instruction Manual            | 732230                 |

| (2) Parallel Interface Cables | 733907                 |

| 1720A PIB Software Disk       | 630699                 |

# **INSTALLATION**

The instructions that follow describe how to install a Parallel Interface option in a 1722A Instrument Controller. Installation into a 1720A Controller is similar; the differences are described in Appendix F, "Using the Parallel Interface with a 1720A".

# **Configuration Procedure**

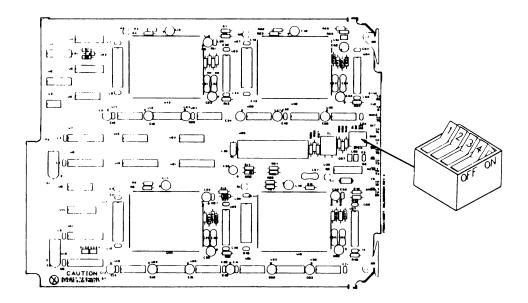

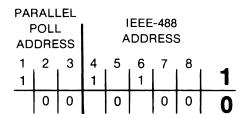

The operating configuration of the Parallel Interface is set up by a board address switch and a configuration jumper block on the module. The information here describes the proper switch settings for various configurations. The Parallel Interface is shipped in the following operating configuration:

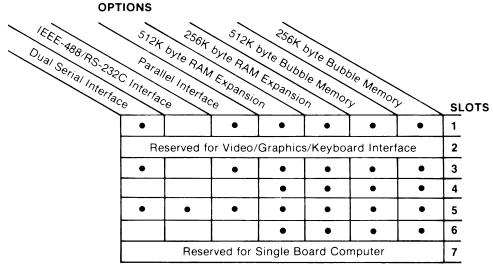

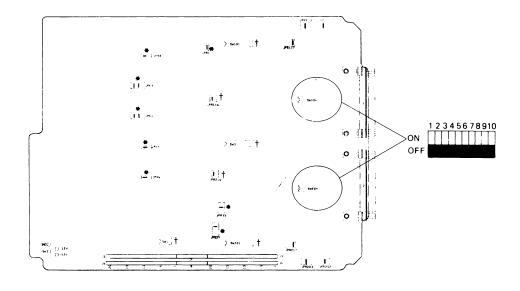

1. Set the address switch for ports PI0 and PI1. Use the table below to ensure that the switch is set properly for port addressability.

**Switch/Address Operating Configuration**

| BOARD | SW4 | SW3 | SW2  | SW1 | PORT<br>PI0 | ADDRESS<br>PI1 | ADDRESS<br>RANGE |

|-------|-----|-----|------|-----|-------------|----------------|------------------|

| 1     | N   | ΟŇ  | ON   | ON  | 0           | 1              | F340-F346        |

| 2     | 0   | ON  | ON   | OFF | 2           | 3              | F348-F34E        |

| 3     | T   | ON  | OFF  | ON  | 4           | 5              | F350-F356        |

| 4     |     | ON  | OFF" | OFF | 6           | 7              | F358-F35E        |

| 5     | U   | OFF | ON   | ON  | 8           | 9              | F360-F366        |

| 6     | S   | OFF | ON   | OFF | 10          | 11             | F368-F36E        |

| 7     | E   | OFF | OFF  | ON  | 12          | 13             | F370-F376        |

| 8     | ם   | OFF | OFF  | OFF | (14         | 15 ->          | F378-F37E        |

|       |     |     |      |     |             |                |                  |

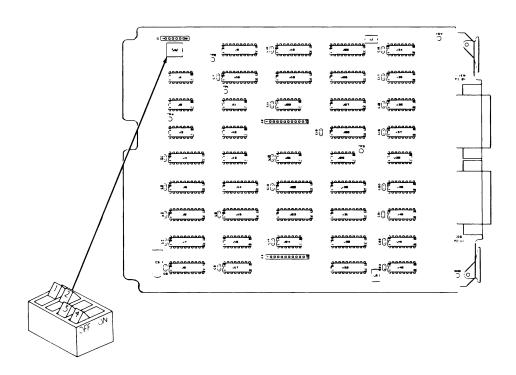

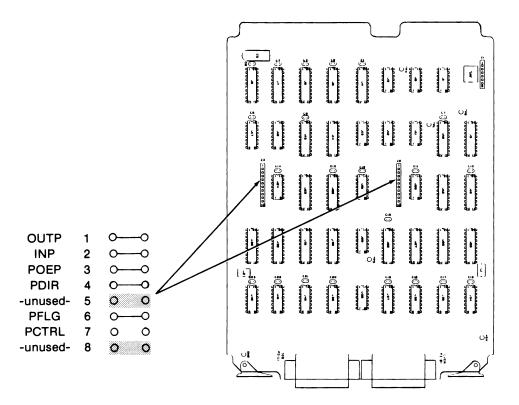

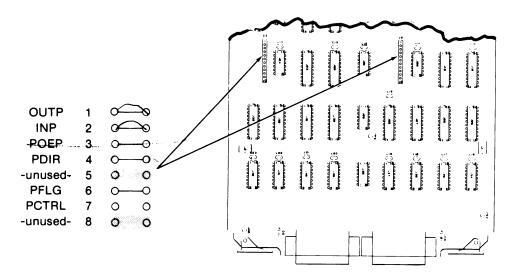

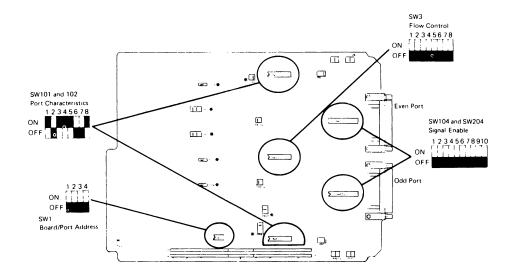

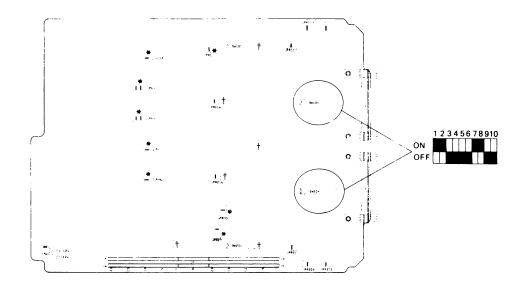

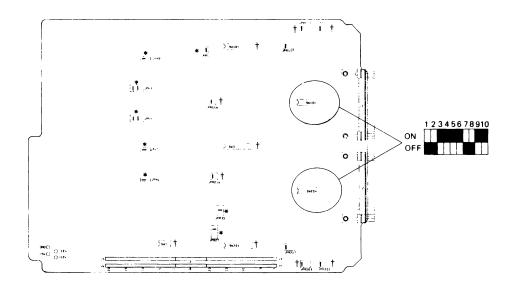

2. Each port also has a configuration jumper block, shown in the illustration below. The shipping configuration is identical for both ports, and is summarized in the table following the illustration.

This table indicates the meanings of each of the jumper positions. Notice that the shipping configuration results in these characteristics:

| NAME                             | SHIPPING CONFIGURATION                                                                                                                                                                                                                                                               |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTP INP POEP PDIRP PFLGP PCTRLP | Jumpered = Normal data output.  Jumpered = Normal data input.  Jumpered = POE HI enables outputs, LO disables them.  Jumpered = PDIR HI for all lines bidirectional, LO for output.  Jumpered = PFLG LO is asserted, HI not asserted.  Open = PCTRL LO is asserted, HI not asserted. |

3. If the shipping configuration is satisfactory, proceed to the Software Compatibility check. If you need to change the shipping configuration, use the table to select the desired operating configuration before proceeding.

### SOFTWARE COMPATIBILITY

For the 1722A Instrument Controller, the Parallel Interface software is supplied on the 1722A System Disk. These machine language programs are interdependent and are compatible only in the combinations of versions supplied by Fluke and documented in published Fluke manuals. Using incompatible system software modules may give unpredictable results. In this case, Fluke cannot provide software support except for identification of compatible combinations.

#### NOTE

The floppy disk supplied with the Parallel Interface option contains software for operating the interface when it is installed in a 1720A Instrument Controller ONLY. The same routines for the 1722A Controller are already supplied on the System Disk that is shipped with the instrument.

There are some important (but easily overlooked) differences between the two sets of routines. For one thing, they are not interchangeable. This manual assumes that the Parallel Interface will be installed into a 1722A. If you are working with the 1720A Instrument Controller, be sure to refer to Appendix F for complete details on using the Parallel Interface with a 1720A Instrument Controller.

Software modules are easily erased and copied, so it is important to record modules onto a disk in the same combinations as they are supplied by Fluke. Place a Write-Protect tab on final disks as added insurance that no incompatible modules are accidentally recorded.

Check that the versions of the system software programs listed table below are the same. For example, all of them should be 1.0, 1.1, 1.2, and so forth. This manual supports system software modules up to and including Version 1.3.

These modules must have the same version numbers:

FDOS.SYS TIME.FD2 SET.FD2 FUP.FD2 BASIC PIBLIB.OBJ

#### NOTE:

As subsequent software releases become available, all version numbers are incremented. If these releases are also supported by this manual, an addendum will be supplied that identifies the compatible versions and any functional changes and additions.

### INSTALLATION PROCEDURE

After setting the switches and jumpers, and confirming software compatibility, follow these steps to install the Parallel Interface module in the 1722A Instrument Controller. Installation instructions for the 1720A are given in Appendix F.

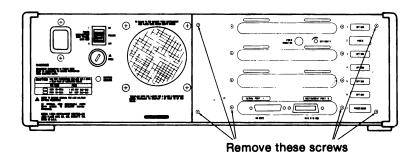

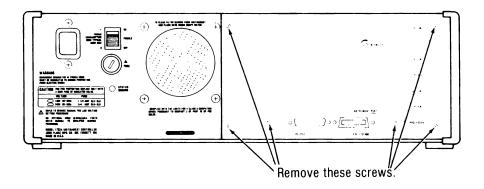

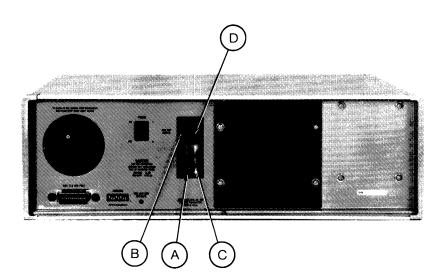

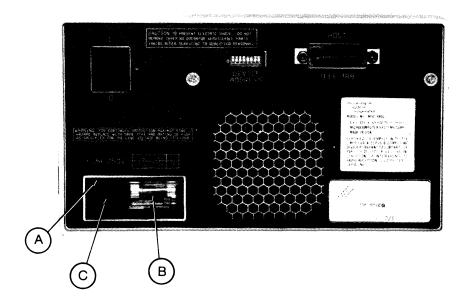

- 1. Power down the Controller, and remove the line cord.

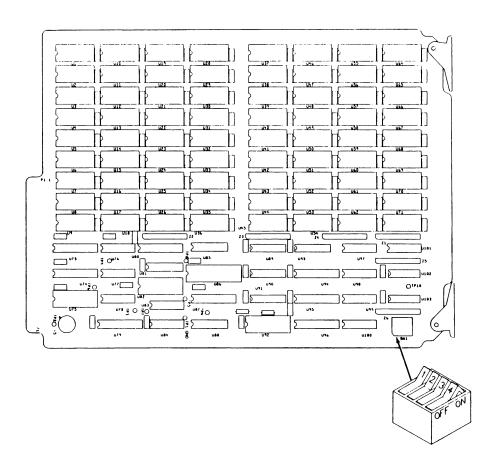

- 2. Remove the rear card cage cover, illustrated below. Depending on which modules are already installed, more screws than those indicated may also have to be removed. The six screws shown here are those that are removed from a new Controller with no options installed.

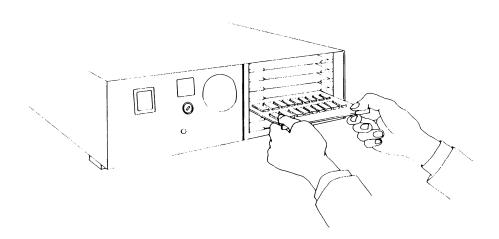

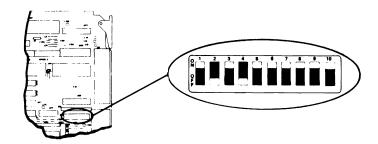

3. Carefully slide the option module into slot 1, 3, or 5 in the card cage. Make sure the module is fully seated so that it makes solid contact with the card-edge connector.

- 4. Remove the two screws holding the plate with the oval opening onto the card cage cover. After reinstalling the card cage cover, thread these screws though the card cage cover and into the shield plate surrounding the interface connectors.

- 5. Reinstall the card cage cover and the power cord.

- 6. Once installation is complete, power up the Controller and test the module by running the System Diagnostic "PIBTST". This program, which is part of the System Diagnostics software, verifies that the module is operating properly.

#### NOTE

For more rigorous testing, a loopback connector, John Fluke Part Number 632968, is available that connects the two ports and sends data between them. Listings for two loop-around programs are included in Appendix C.

- 7. Connect the plug of the Parallel Interface Cable to the connector on the Parallel Interface module. Connect the other end of the cable to the instrumentation system. Refer to Section 3, Interface Description, for complete information about the signals carried on each of the lines.

- 8. In case of any problems, recheck your work to ensure that switches are set properly and that the correct jumpers are in place. Be sure that the board is fully seated in the card cage. If everything is in order, but the failure continues, refer to the System Guide, Appendix G, System Diagnostics, for troubleshooting information, or call your local Fluke Service Center.

#### **GETTING STARTED**

Once the interface has been designed, it is a simple matter to use the PIBLIB routines in a program. Here are a few things to keep in mind:

- □ Early in the program, link to the library. In Interpreted BASIC programs, the line reads, LINK "PIBLIB". For other languages, consult the programming manual.

- □ Most of the routines can be used merely by giving the program name followed by any parameters or arguments required. However, using SETBIT in a BASIC program requires the "CALL" statement because of possible ambiguity with other BASIC "SET" statements like "SET SHELL".

- Although it isn't always necessary, make it a practice to use PCLOSE (Close a Port) prior to POPEN (Open a Port), as a housekeeping measure. No errors result from closing an already closed port, but errors are reported if you try to open a port that is already open.

- Be sure to include a CTRL/C handler in all programs. When  $\langle CTRL \rangle / C$  is pressed, close the ports to ensure that no errors occur the next time you run the program.

The most important thing to keep in mind as you begin the design is to carefully outline the requirements of the intended system before beginning. This task breaks conveniently into two parts. First determine the direction, polarity, and level of the data lines, and of the handshake lines if they will be used. Begin software design only after the hardware requirements have been defined.

Finally, remember that the Option 17XXA-002 is an extremely versatile addition to the Fluke Instrument Controller. The PIB has the built-in ability to adapt to some of the most unusual interface requirements of the connected device(s).

# Section 3 Interface Description

| CONTENTS                              |              |

|---------------------------------------|--------------|

|                                       |              |

|                                       | 3-2          |

| 1                                     | 3-3          |

|                                       | 3-3          |

|                                       | 3-3          |

|                                       | <b>3-6</b>   |

|                                       | 3-8          |

| Port Direction Line (PDIR)            | 3-8          |

| Port Output Enable Line (POE)         | 3-10         |

|                                       | 3-11         |

|                                       | 3-14         |

| Typical Transmitter Circuits          | 3-14         |

|                                       | 3-15         |

|                                       | 3-17         |

|                                       | 3-17         |

|                                       | 3-19         |

|                                       | 3-21         |

|                                       | 3-23         |

| 1                                     | 3-24         |

| • • • • • • • • • • • • • • • • • • • | 3-25         |

|                                       | 3-27         |

| Mode 3 - Strobe Output Handshake      | 3-29         |

|                                       | 3-30         |

|                                       | 3-31         |

|                                       | 3-31         |

|                                       | 3-31<br>3-32 |

|                                       | 3-32<br>3-33 |

|                                       |              |

| FORTRAN Programs                      | 3-34         |

### INTRODUCTION

The information in this section describes the hardware interface, the interface cable, and the software protocols. The hardware interface information defines in detail the port lines and illustrates a few typical handshake configurations and interfacing circuits.

The software protocol descriptions show the timing of each of the handshake modes in a reference page format. In most cases, timing is not crucial; this information is included to assist those who design systems where timing is a concern.

The section ends with some notes on using the timeout mechanism and interrupts. The software library is described in the next section.

#### HARDWARE INTERFACE DESCRIPTION

This section describes the hardware interface and the signals that the Parallel Interface sends and receives.

#### **Port Lines**

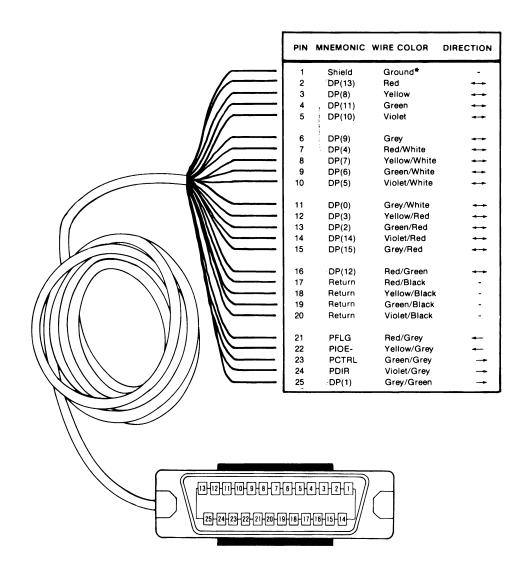

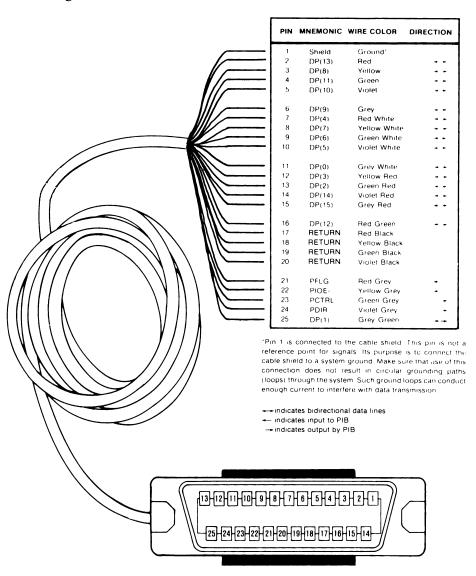

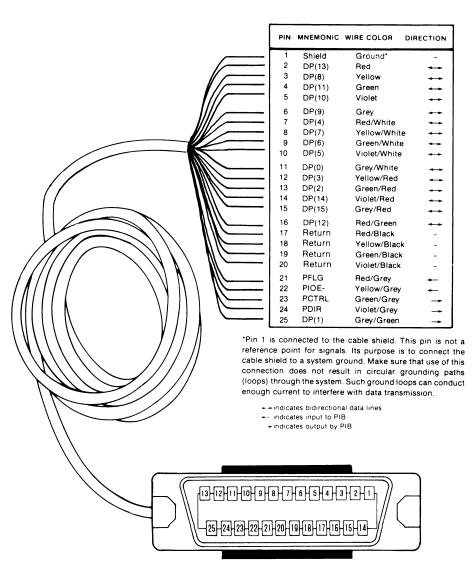

The port lines provide bidirectional data transmission between the Instrument Controller and compatible external devices. The drawing below shows the connector and lists the signal definition and logic states for each of the lines at the interface.

# **Port Signals**

On the Parallel Interface module, several signals control the direction of data and the sense of the handshake lines. These signals, and the jumpers which can invert them, are defined in the following tables. Notice that by reconfiguring the jumpers, the handshake can be fully or partly inverted.

\*Pin 1 is connected to the cable shield. This pin is not a reference point for signals. Its purpose is to connect the cable shield to a system ground. Make sure that use of this connection does not result in circular grounding paths (loops) through the system. Such ground loops can conduct enough current to interfere with data transmission.

<sup>---</sup> indicates bidirectional data lines

<sup>-</sup> indicates input to PIB

<sup>→</sup>indicates output by PIB

## **Port Signal Definitions**

| SIGNAL NAME   | DIRECTION          | DEFINITION                                                                                                                                                                                                                                                                                                                                                           |

|---------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDIR          | Output             | Port Direction: Direction of data on port.                                                                                                                                                                                                                                                                                                                           |

|               |                    | Logic I = all lines bidirectional or input only Logic $0 = all$ lines output                                                                                                                                                                                                                                                                                         |

| POE           | Input              | Port Output Enable: Used by external device to disable the output from the ports. This is done typically if the device is sending data to the port.                                                                                                                                                                                                                  |

|               |                    | Logic I = outputs enabled<br>Logic 0 = outputs disabled                                                                                                                                                                                                                                                                                                              |

| PFLG          | Input              | Port Flag: One of the two handshake lines; the signal originates with the peripheral device. For input operations (device to port), PFLG, when asserted, indicates that input data is valid. For output operations, PFLG, when asserted, acknowledges that the device is reading the output data from the port.                                                      |

| PCTRL         | Output             | Port Control: One of the two handshake lines; the signal originates with the Parallel Interface module. For output operations (port to external device), PCTRL, when asserted, indicates that the output data is valid and the device may read it. For input operations, PCTRL, when asserted, indicates that the port is reading the incoming data from the device. |

| Data<br>Lines | Bidirec-<br>tional | Each data line can be used either as an input or as an output. For a full discussion, please refer to the discussion of the Direction Mask in Section 4.                                                                                                                                                                                                             |

# **Port Control Jumpers**

Each port has a configuration jumper block, shown in the illustration below. The shipping configuration is identical for both ports, and is summarized in the table following the illustration.

**Port Signal Definitions**

| JUMPER | DEFINITIONS                                                                                                                                                                                                                                |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCTRP  | Port Control Polarity: Controls the sense of PCTRL. When the jumper is removed (default):                                                                                                                                                  |

|        | Logic I = PCTRL is not asserted Logic O = PCTRL is asserted                                                                                                                                                                                |

|        | When the jumper is in place:                                                                                                                                                                                                               |

|        | Logic I = PCTRL is asserted Logic O = PCTRL is not asserted                                                                                                                                                                                |

| INP    | Input Polarity: At the software's option, allows data to be inverted before it is input. When the jumper is in place (default), input data is not inverted. When the jumper position is open, the input data is inverted after being read. |

OUTP

Output Polarity: At the software's option, allows data to be inverted before output. When the jumper is in place (default), output data is not inverted; when the jumper position is open, the output data is inverted.

PDIRP

Port Direction Polarity: Inverts the sense of PDIR. When the jumper is in place (default), the sense of PDIR is defined as:

Logic I = all lines bidirectional or input only Logic O = all lines are output only

When the jumper is open, the sense of PDIR is defined as:

Logic I = all lines are output only Logic O = all lines are bidirectional or input only

Logic I = outputs enabled Logic O = outputs disabled

POEP

Port Output Enable Polarity: Inverts the sense of POE. When the jumper is in place (default), the sense of POE is defined as:

Logic I = outputs enabled Logic O = outputs disabled

When the POEP jumper position is open, the sense of POE is defined as:

Logic I = outputs disabled Logic O = outputs enabled

**PFLGP**

Port Flag Polarity: Controls the sense of PFLG.

When the jumper is in place (default):

Logic I = PFLG is asserted

Logic O = PFLG is not asserted

When the jumper is removed:

Logic I = PFLG is not asserted

Logic O = PFLG is asserted

#### **Notes on the Port Control Lines**

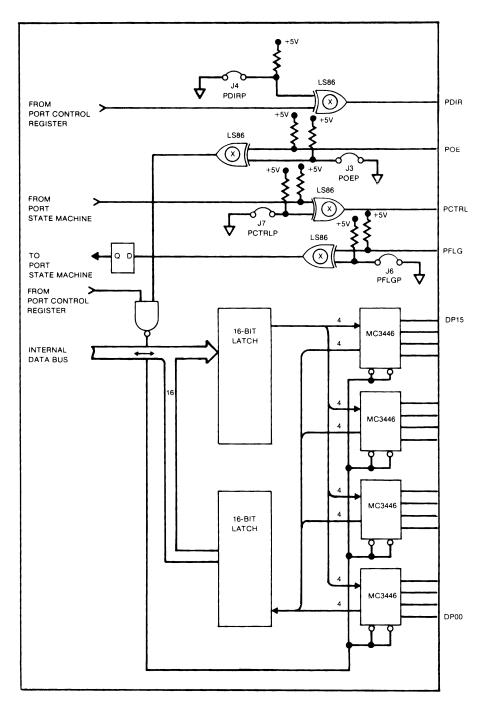

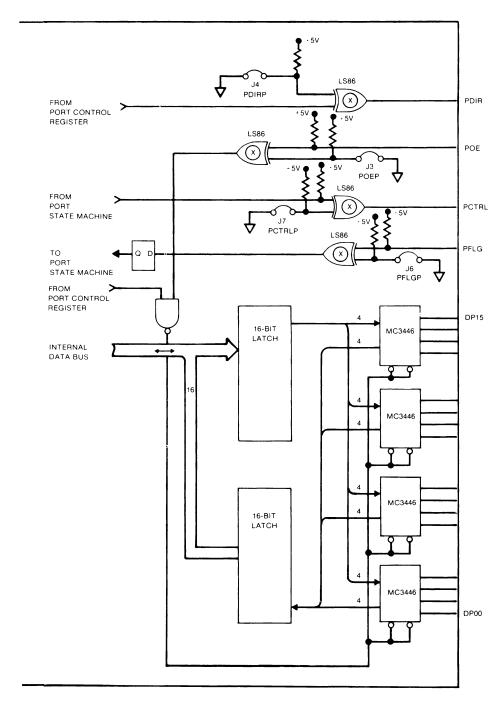

For this discussion, refer to the illustration on the next page. Each port consists of 16 data lines and 4 control lines. The control lines PCTRL and PFLG are used for handshake operation and are only active during Modes 1, 2, and 3 (not in Mode 0). The normal sense of these signals is active low. Their sense can be inverted by the PCTRP and PFLGP jumpers.

The other control lines, PDIR and POE (Port Direction and Port Output Enable) can be sensed or controlled by the external peripheral. When a port is opened using the POPEN command, the data lines are initially reset to logic high levels.

## Port Direction Line (PDIR)

The Port Direction line is set to either a logic high or a logic low when the port is opened. If the port is opened in Modes 0 or 1, PDIR is set to a logic 1; if it is opened in Modes 2 or 3, the direction line is set to 0, and the polarity will not change unless the port is closed and reopened in another mode. See the table below. When the port is closed, PDIR is reset to 0.

| PDIR |

|------|

| 1    |

| 0    |

| l    |

|      |

The handshake modes are described fully later in this section.

# Port Output Enable Line (POE)

The Port Output Enable line enables and disables the output drivers. It is controllable by the external device. The MC3446A transceiver can be set to operate as a transparent buffer, or can be disabled. If it is disabled, the data lines are pulled to a logic high, the condition when the port is opened or closed. The MC3446A is not a tristate device. This means that the transceiver is never put into a high-impedance state; the port is always either sinking or sourcing current on the data lines.

The following table summarizes the actions the external device can affect on the transceivers by manipulating the POE line.

| POE FROM EXTERNAL DEVICE | ACTION                                                         |

|--------------------------|----------------------------------------------------------------|

| Logic High               | Enables outputs. Outputs reflect state of registered data.     |

| Logic Low                | Disable outputs. Outputs are pulled to a logic high.           |

| No Connection            | POE pulled to logic high; there-<br>fore, outputs are enabled. |

#### INTERFACE CIRCUITS

The next few pages illustrate some typical interface circuits. Note that John Fluke Mfg. Co. does not guarantee these circuits for any particular application, and is not liable for their use. The component values shown are typical, and may have to be adjusted in the actual implementation.

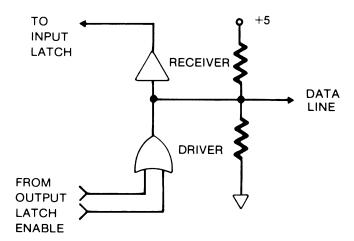

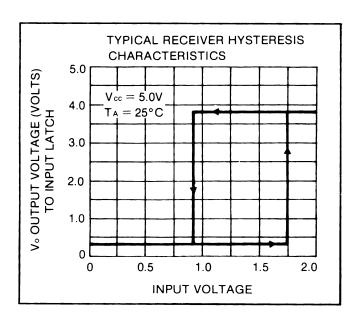

The Parallel Interface data lines are driven by the Motorola MC3446A Transceiver. This component is compatible with RTL, DTL, TTL, and MOS devices. It also meets the requirements of the IEEE-488-1978 standard. Some critical electrical specifications of the MC3446A are illustrated on the next page.

#### MC 3446 DATA LINE INTERFACE CIRCUITRY

#### MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise noted.)

| RATING                | SYMBOL        | VALUE | UNIT |

|-----------------------|---------------|-------|------|

| Input Voltage         | V١            | 5.5   | Vdc  |

| Driver Output Current | <b>1</b> 0(D) | 150   | mA   |

#### **ELECTRICAL CHARACTERISTICS**

| CHARACTERISTIC                                                                                                      | MIN      | TYP  | XAM   | UNIT |

|---------------------------------------------------------------------------------------------------------------------|----------|------|-------|------|

| DRIVER PORTION                                                                                                      |          |      |       |      |

| Input Voltage — High Logic State                                                                                    | 2.0      | _    | _     | ٧    |

| Input Voltage — Low Logic State                                                                                     | <b> </b> | _    | 0.8   | V    |

| Input Current — High Logic State<br>(V <sub>IH</sub> = 2.4V)                                                        | _        | 5.0  | 40    | μΑ   |

| Input Current — Low Logic State $(V_{IL} = 0.4 \text{ V}, V_{CC} = 5.0 \text{V}, T_A = 25^{\circ}\text{C})$         |          | -0.2 | -0.25 | mA   |

| Output Voltage — High Logic State (1) (V <sub>IH(S)</sub> = 2.4V or V <sub>IH(D)</sub> = 2.0V)                      | 2.5      | 3.3  | 3.7   | V    |

| Output Voltage — Low Logic State (V <sub>IL(S)</sub> = 0.8V, V <sub>IL(D)</sub> = 0.8V, I <sub>OL(D)</sub> = 48 mA) |          | _    | 0.5   |      |

| RECEIVER PORTION                                                                                                    |          |      |       |      |

| Input Hysteresis                                                                                                    | 400      | 625  | _     | mV   |

| Input Threshold Voltage  — Low to High Output Logic State                                                           | _        | 1.66 | 2.0   | ٧    |

| Input Threshold Voltage  — High to Low Output Logic State                                                           | 0.8      | 1.03 | _     | ٧    |

| Output Voltage — High Logic State (V <sub>IH(R)</sub> = 2.0V, I <sub>OH(R)</sub> = -400 $\mu$ A)                    | 2.4      | _    | _     | V    |

| Output Voltage — Low Logic State $(V_{IL(R)} = 0.8V, I_{OL(R)} = 8.0 \text{ mA})$                                   | _        | _    | 0.5   | ٧    |

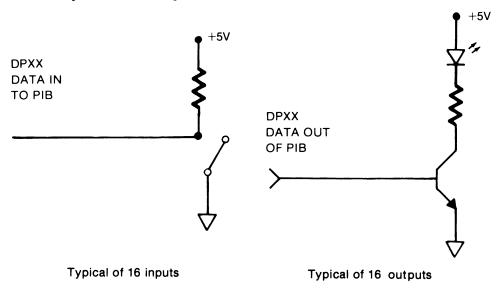

#### **Typical Receiver Circuit**

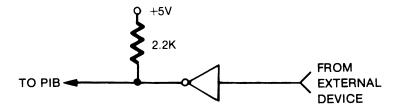

The connected device is receiving the signal(s) from the PIB and represents one TTL load.

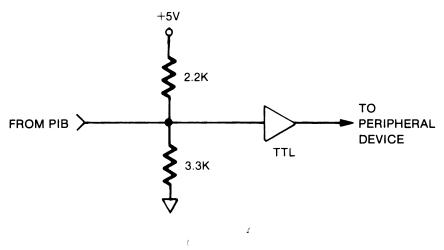

#### **Typical Transmitter Circuits**

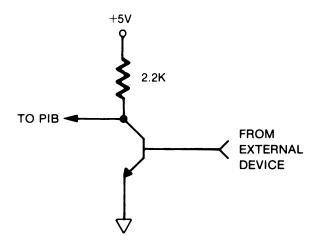

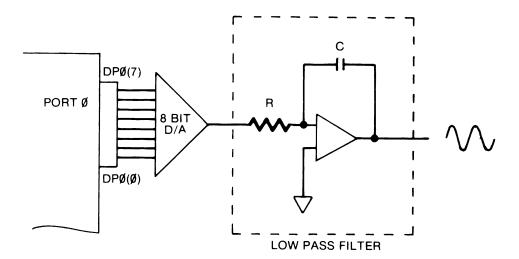

The external device is transmitting at TTL levels.

The peripheral device is transmitting using an open collector device.

The peripheral device has an undefined output level. This circuit ensures that the signal approximates the desirable TTL level of the PIB input. Remember that this circuit inverts the sense of the signal applied to the transistor's base.

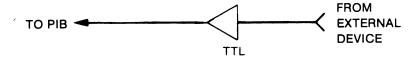

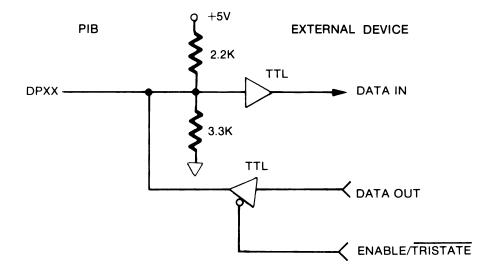

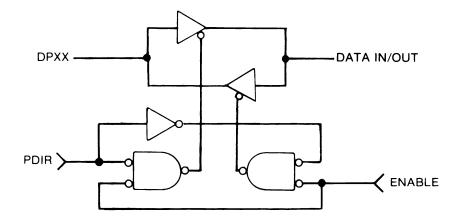

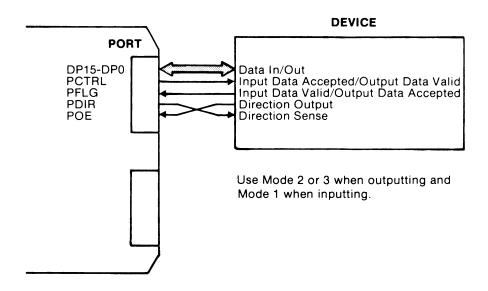

#### **Transceiver for Bidirectional Data Transfer**

This transceiver circuit uses the Parallel Interface module's Port Direction signal FDIR and ENABLE signal at the external device to control tristating of the external device transmitter and reciver.

#### HANDSHAKE MODES

The Parallel Interface module operates in one of four modes: No Handshake, Full Handshake, and Strobe Input and Output. With the exception of No Handshake, the handshakes synchronize incoming and outgoing data. The table below lists the handshake names and the mode number that the software recognizes. Timing diagrams later in this section illustrate the timing requirements of each of the modes.

#### Handshake Modes

| NAME         | DEFINITION            | MODE |

|--------------|-----------------------|------|

| <del>-</del> | No Handshake          | 0    |

| HNDSHKIN     | Full Handshake Input  | 1    |

| STROBEIN     | Strobe Input          | 1    |

| HNDSHKOUT    | Full Handshake Output | 2    |

| STROBEOUT    | Strobe Output         | 3    |

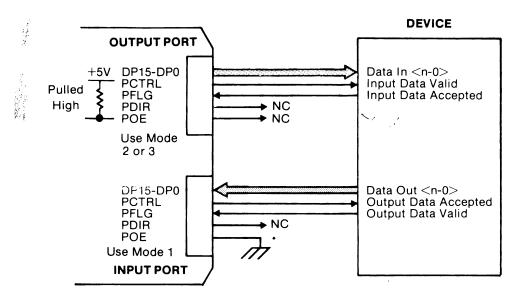

#### **Handshake Configuration Examples**

The drawings that follow illustrate two possible connection methods and show the modes that would be used for them

$\mathcal{M}_i$

\*POE is grounded to force the output devices off since this port is input only.

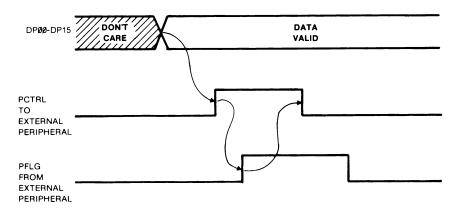

#### Introduction to the Handshake Timing Diagrams

The pages that follow describe the timing of each of the handshakes. Some of the terms used in these diagrams may not be familiar or in general use, so they are defined here:

tresp Response time, the time between an event and the response.

This may be the time that the port takes to respond to a device initiating a handshake, or the time it takes the device to respond to a port-initiated handshake.

tin Input time, the length of time that the port will hold the Handshake Line PCTRL active, or the length of time the external device holds PFLG active. During tin, the CPU or the peripheral device is reading data.

Ready time, the length of time until the port is ready after completion of the last event of the handshake.

tstrobe The pulse width of a pulse or strobe in Modes 2 and 3 (HNDSHKOUT and STROBEOUT). tstrobe is 200 ns minimum.

tw Strobe width time. In Mode 3, the width of the pulse generated by PCTRL. It is 670 ns in duration.

device (CPU or external peripheral) acknowledges that data has been transferred.

# NO HANDSHAKE Mode 0

In the most simple mode, there is no handshaking, so no timing diagram is needed. The handshake lines remain idle, and the interface latches new data when the basic statement is executed.

In this mode of operation, the handshake lines PFLG and PCTRL are not asserted. When a call is made to a port in Mode 0, the data at the port is latched either in or out, depending upon whether the data is read from or written to the port.

The port must be opened in Mode 0. The port will not time out in Mode 0, and there will be no interrupts.

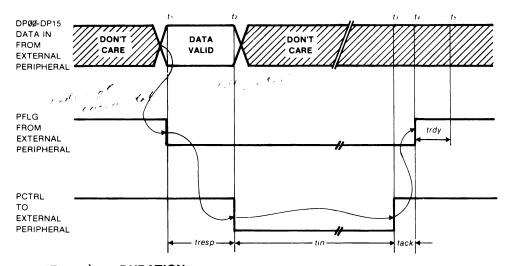

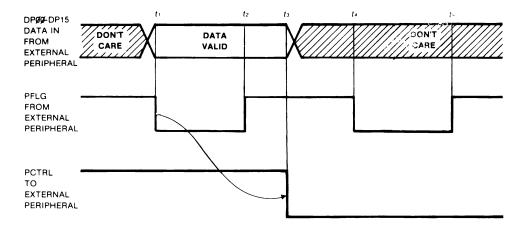

# √ HANDSHAKE INPUT Mode 1

| EVENT | DURATION                        |

|-------|---------------------------------|

| tresp | 670 ns maximum, no minimum.     |

| tin   | 24 $\mu$ s maximum, no minimum. |

| tack  | no maximum.                     |

| trdy  | 200 ns maximum, no minimum.     |

- t1 Data should be valid at the time that PFLG goes active.

- The port responds within 670 ns by making PCTRL active. This indicates that the data has been latched and that the CPU has been notified. However, note that the CPU has not yet read the data. Between times t2 and t3, PCTRL remains active until the CPU reads the data from the latch.

- t3 PCTRL is deasserted indicating to the peripheral device that the data has now been stored. The port will wait until PFLG has deasserted itself, if it hasn't yet done so.

- *t4* PFLG deasserts itself, and the port resets. The handshake is now complete.

- Since it has been reset, the port is now ready for another handshake.

Note that unless the port is transferring data in the Block Mode, the next handshake will not begin until another call to the driver subroutine is made.

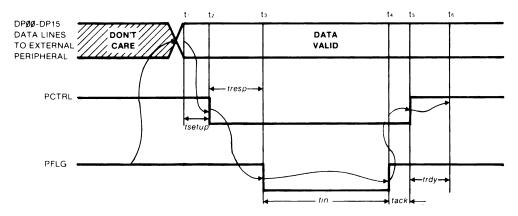

### HANDSHAKE INPUT Mode 1

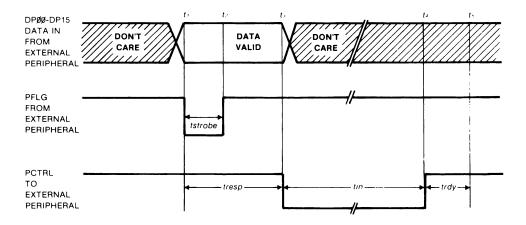

#### Using Mode 1 to Strobe Data into the Port

It is not necessary to use the full handshake to transfer data to the port. The port also recognizes a pulse on the PFLG line. The minimum duration of the strobe is 200 ns. This method of using Mode 1 is illustrated below:

| EVENT   | DURATION                        |  |  |

|---------|---------------------------------|--|--|

| tstrobe | 200 ns minimum.                 |  |  |

| tresp   | 670 ns maximum.                 |  |  |

| tin     | 24 $\mu$ s maximum, no minimum. |  |  |

| trdy    | 200 ns maximum, no minimum.     |  |  |

- The peripheral device has valid data, and therefore initiates the handshake by setting PFLG low. Since it is only strobing the port, it deasserts PFLG at time t2. In order for the port to recognize it, the length of strobe must be > 200 ns.

- t2 The peripheral device deasserts PFLG. Data has been valid for at least 200 ns.

- t3 The CPU has responded to the strobe and has latched the data.

- After tin, the CPU has finished transferring the data, and PCTRL is deasserted. The port checks the status of PFLG to see that it was deasserted.

### HANDSHAKE INPUT Mode 1

#### **Peripheral Device Strobing Too Rapidly**

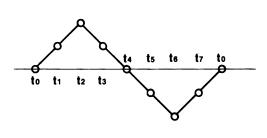

It is very important that the strobe rate of the peripheral device does not exceed the speed of the port because data can be lost. To ensure that PCTRL has been deasserted before attempting another data transfer, the external peripheral must either monitor the PCTRL line, or it must use an interval timer of at least *tin* duration. Here is an example of a peripheral device attempting to send data too rapidly.

By strobing PFLG at t1, the peripheral device has notified the port that there is valid data. The port proceeds with the handshake and by time t3, the data has been latched.

However, the peripheral device doesn't wait for the CPU to read the latch and for the handshake to end with PCTRL being deasserted. Instead, the peripheral strobes PFLG again at time 14. The port is not available for data transfers while PCTRL is active, so it misses this new piece of data because the CPU is still busy attempting to read the original data.

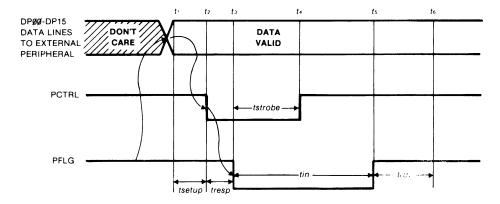

# HANDSHAKE OUTPUT Mode 2

| EVENT  | DURATION                                |  |  |

|--------|-----------------------------------------|--|--|

| tsetup | 200 ns maximum, no minimum.             |  |  |

| tresp  | Depends on external device; no maximum. |  |  |

| tack   | 200 ns maximum.                         |  |  |

| tin    | Depends on external device; no maximum. |  |  |

| trdy   | 200 ns maximum.                         |  |  |

- Before registering valid data, the port checks the state of the PFLG line. If PFLG is inactive, the port proceeds to latch the valid data.

- The port initiates the handshake at time t2 by setting PCTRL low, indicating to the peripheral device that valid data is available and latched at the port.

- From this point on, the port operates autonomously without CPU monitoring. The peripheral responds to the new state of PCTRL by setting PFLG low. This event may occur before tresp (~400 ns). However, the port only recognizes that PFLG has gone active no sooner than 400 ns after PCTRL has become active.

There is no maximum time period for tresp. The port continues to monitor the PFLG line until PFLG goes active. After response time tresp, the peripheral device holds PFLG active for at least the data input time (tin),  $\sim 200$  ns in order for this signal to be recognized.

### HANDSHAKE INPUT Mode 2

- The peripheral device allows PLFG to go inactive. Within 200 ns, the port makes PCTRL inactive at time t5.

- the port is available again for handshaking no later than trdy at time the, a maximum of 200 ns after the that this event only signifies the end of the handshake. Another handshake will only begin if the port is transferring blocks of data using WTBLK or FWTBLK. Otherwise, another transfer will occur when WTWRD is called from the calling program.

# STROBE OUTPUT HANDSHAKE Mode 3

| EVENT   | DURATION                                |

|---------|-----------------------------------------|

| tsetup  | 200 ns maximum, no minimum.             |

| tresp   | Depends on external device; no maximum. |

| tstrobe | 400 ns maximum.                         |

| tin     | Depends on external device; no maximum. |

| trdy    | 200 ns maximum.                         |

- t1 The port latches valid data.

- t2 The port makes PCTRL active, indicating that new data has been latched.

- The peripheral device recognizes that the port has initiated a handshake, and responds by setting PFLG active.

PFLG may be brought active low before *tresp*. However, it will not be recognized by the port sooner than 400 ns after PCTRL is first made low. Also, PFLG must remain low for at least 200 ns to guarantee that the port recognizes the new state.

PCTRL returns to its inactive state no later than 400 ns after PFLG becomes active. After it has finished reading data, the external peripheral resets the PFLG line to its inactive state. The port recognizes this action, and after trdy (200 ns) is again available for data transfer.

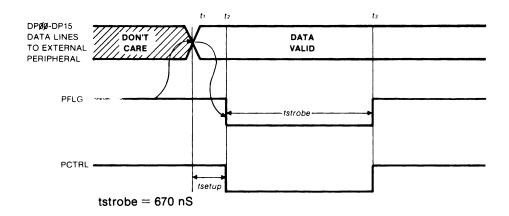

# STROBE OUTPUT HANDSHAKE Mode 3

#### **Using Mode 3 for Partial Handshake Operation**

By physically tying the PCTRL and PFLG lines to one another, the port can be configured to operate in a partial handshake mode.

In this mode of operation, a strobe of 670 ns duration indicates to the peripheral device that valid data has been latched and is available. It is not a full handshake because PFLG is already active, and the port does not wait to receive it as the indication that the peripheral is ready.

## SOME NOTES ON USING THE PARALLEL INTERFACE BOARD Inverting the Handshakes

Before it is shipped, the Parallel Interface module is configured for the handshake lines PFLG and PCTRL to operate active low. This means that in their active states, these signals are at a logic low, and when they are inactive, they are at a logic high.

The handshakes can be configured by jumpers to operate either active high or active low. As an example, to configure Port 0 to handshake active high, cut the PFLGP jumper, and place a jumper on PCTRLP. If this is done, the timing diagram below illustrates the Mode 3 Strobeout active high handshake.

**EXAMPLE OF INVERTED STROBE OUTPUT HANDSHAKE**

#### **Timeout Mechanism**

The timeout mechanism provides a way to recover from an incomplete handshake after a time period specified by the software. The timeout mechanism operates differently for the different handshake modes. The timeout error is recoverable.

□ Mode 0

In Mode 0, No Handshake, the port never times out. Data is read from and written to the port regardless of the states of the handshake lines.

□ Mode 1

In Mode 1, Handshake Input, the port times out if the peripheral device does not initiate a handshake by making PFLG active within the specified timeout period.

□ Modes 2 and 3

When writing to a port in Mode 2 or Mode 3 (Handshake Output), the software first checks the port to determine whether the last handshake has been completed. The software continually checks the port until either the last handshake is complete (in which case a new handshake begins), or until the specified timeout period ends with the last handshake still incomplete. If the second case occurs, a timeout error is reported.

#### Using Interrupts to Drive the Parallel Interface

When working with slow peripheral devices, it is possible to use the Parallel Interface module in an interrupt-driven mode. Doing so requires that the Port Mode parameter be set up properly. For more information, see the discussion of parameters in Section 4. A port-to-port loop program using interrupts is shown in Appendix C, Sample Programs.

In the interrupt-driven method of operation, the Instrument Controller can be freed to do other tasks while it is collecting data from the Parallel Interface in a "background" process, thus allowing some degree of parallel processing.

To operate in the interrupt-driven mode, use the BASIC statement

```

ON PPORT GOTO (linenumber)

```

The OFF PPORT statement disables interrupts from the PIB. For complete information on how to use these statements in a BASIC program, see the BASIC Reference Manual, reference entries 96 (ON PPORT), and 84 (OFF PPORT).

In addition, the mode parameter of the POPEN statement must be set appropriately. See the discussion on parameters in Section 4.

In Mode 1, when the PIB senses that PFLG has been asserted, it latches the data and simultaneously notifies the CPU via interrupt that new data is available. When the BASIC Interpreter is notified, it finishes executing the current command and jumps to the interrupt handler subroutine in this fashion:

```

100 ! Interrupt Handler for P.I.B.

110 RDWRD (parameters)

120 !

130 ! — code for processing data —

140 !

150 !

150 !

160 RESUME ! return to main program

```

Interrupts can be used in Mode 2 or Mode 3 to indicate the end of a handshake. After outputting a data word to a port, the driver software does not wait for the handshake to complete. Instead, it returns to the next BASIC statement. The interrupt can be used to indicate that another data transfer can be made.

#### **FORTRAN Programs**

FORTRAN does not handle interrupts. Therefore, the PIB cannot be used in the interrupt-driven mode if the Controller's programs are written in FORTRAN. This is one of the reasons that a FORTRAN program executes so quickly. A FORTRAN program does not have the time-consuming overhead necessary for interrupt handling.

# Section 4 Parallel Interface Board Library (PIBLIB.OBJ)

#### **CONTENTS**

| Introduction                                         | 4-3  |

|------------------------------------------------------|------|

| Subroutine Summary                                   | 4-3  |

| Parameters                                           | 4-4  |

| Integer Equivalents of Binary Numbers                | 4-6  |

| Example 1. Converting A Binary Digit to an Integer   |      |

| (Direction Mask)                                     | 4-6  |

| Example 2. Converting an Integer to a Binary Number. | 4-7  |

| Event Interrupts                                     | 4-8  |

| Program Examples                                     | 4-8  |

| Subroutine Reference Pages                           | 4-9  |

| CHKBIT                                               | 4-9  |

| CLRBIT                                               | 4-11 |

| SETBIT                                               | 4-13 |

| RDWRD                                                | 4-15 |

| WTWRD                                                | 4-17 |

|                                                      | 4-19 |

|                                                      | 4-19 |

|                                                      |      |

| FRDBLK                                               | 4-23 |

| FWTBLK                                               | 4-25 |

| POPEN                                                | 4-27 |

| PCLOSE                                               | 4-29 |

| Error Messages                                       | 4-30 |

#### INTRODUCTION

This section presents each of the subroutines in the 17XXA-002 Parallel Interface Board Library (PIBLIB.OBJ). The subroutines are alphabetically arranged and described in a reference page format. Error messages that might be returned for each routine are included as a part of the reference page, and are also given in a table at the end of this section.

#### **Subroutine Summary**

This table summarizes each of the routines in the Parallel Interface Board Library. A full discussion with program examples can be found in reference pages at the end of this section. All parameters are integers.

#### **Summary of PIBLIB Routines**

| SUBROUTINE | DESCRIPTION                   | PARAMETERS                |

|------------|-------------------------------|---------------------------|

| СНКВІТ     | Check a bit                   | Port, Bit, Bool           |

| CLRBIT     | Clear a bit on a port         | Port, Bit                 |

| SETBIT     | Set a bit on a port           | Port, Bit                 |

| RDWORD     | Read word at a port           | Port, Word                |

| WTWORD     | Write a word to a port        | Port, Word                |

| RDBLK      | Read to a port from an array  | Port, Block, Count        |

| WTBLK      | Write to a port from an array | Port, Block, Count        |

| FRDBLK     | Same as RDBLK, but faster     | Port, Block, Count        |

| FWTBLK     | Same as WTBLK, but faster     | Port, Block, Count        |

| POPEN      | Open a port                   | Port, Mode, Mask, Timeout |

| PCLOSE     | Close a port                  | Port                      |

#### **Parameters**

When the routines are used in a program, one or more parameters are specified by the programmer. All parameters must be specified as integers. The reference page for each routine includes the required parameters, which are defined below.

**PORT**

The port number for the routine to operate on, expressed as an integer in the range 0 - 15. Use the table below to assign port numbers to any number of Parallel Interface modules.

| BOARD | PORTS  |

|-------|--------|

| 0     | 0, 1   |

| 1     | 2, 3   |

| 2     | 4, 5   |

| 3     | 6, 7   |

| 4     | 8, 9   |

| 5     | 10, 11 |

| 6     | 12, 13 |

| 7     | 14, 15 |

4

MODE

The mode parameter consists of two one-byte parameters in a 16-bit integer. The high order byte determines whether or not interrupts from the interface will be acknowledged by the Controller (using the ON PPORT command in BASIC, for example). The low order byte determines the mode of operation.

High Order Byte: set to one (1) to enable interrupts from the PIB, and zero (0) to disable them. This is easily accomplished in decimal by adding 256 to the low order byte. This example opens Port 0 in the No Handshake mode with interrupts enabled, all bits input, and a timeout of 2 seconds:

POPEN (0%, 256% + 1%, -1%, 200%)

Lower Order Byte: indicates the mode of operation as shown below. For more information, see Section 3.

| VALUE | NAME              | DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0     | No Handshake      | Bidirectional input and output with no handshakir PCTRL and PFLG remain inactive.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 1     | Hndshkin          | Handshake input. Handshaking under control of PCTRL and PFLG.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 2     | Hndshkout         | Handshake output. Handshaking under control of PCTRL and PFLG.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 3     | Strobeout         | Strobe handshake output.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|       | TIME OUT          | The wait time before an incomplete handshake is terminated. Timeout is a programmable integer in the range 0 - 32767; each count is one 10-millisecond "tick". The longest timeout, 32767 x 10 ms = 328 seconds, or about five and a half minutes. Specifying 0 disables timeout.                                                                                                                                                                 |  |  |  |  |  |

|       | BIT               | The bit number to be checked, read, or written to, expressed as an integer. The least significant bit is 0 and the most significant bit is 15.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|       | BOOL              | When a bit or word is read or checked, as in the CHKBIT routine, the routine returns the value into a variable specified as BOOL. This value is an integer in the range of 0 to 32768, corresponding to bool = $2^n$ , where n is the bit position. This variable can be used in Boolean expressions, because its value will always be either zero or non-zero.                                                                                   |  |  |  |  |  |

|       | DIRECTION<br>MASK | An integer that indicates the desired transmission direction of each bit on the port. The Direction Mask is the decimal equivalent of the two's complement of the binary number. Input lines are encoded as 1-bits and outputs as 0-bits. If the port is to be used for output only, the direction mask parameter would be set to 0. For input on all lines, use -1. The Direction Mask insures that an input bit is not driven as an output bit. |  |  |  |  |  |

For more detail, Example 2 (following) shows how to convert a binary word to a decimal integer.

BLOCK This parameter is the array to which data will be

transferred using the Block subroutines (RDBLK, WTBLK, FRDBLK, and FWTBLK.)

COUNT Indicates how many array elements to transfer.

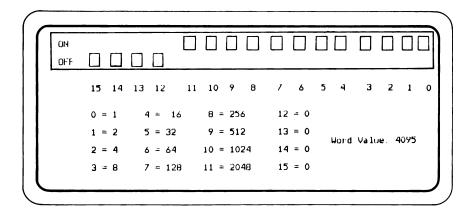

#### **Integer Equivalents of Binary Numbers**

During programming the Parallel Interface, it is often necessary to convert a 16-bit binary word to a decimal integer, and vice versa. Use the table below to decode BOOL and to assist in calculating the integer to be used for various direction masks.

| 215   | 214   | 213  | 212  | 211  | 210  | 2 <sup>9</sup> | 2 <sup>8</sup> | 27  | 2 <sup>6</sup> | 25 | 24 | 23 | 22 | 21 | 20 |

|-------|-------|------|------|------|------|----------------|----------------|-----|----------------|----|----|----|----|----|----|

| 32768 | 16384 | 8192 | 4096 | 2048 | 1024 | 512            | 256            | 128 | 64             | 32 | 16 | 8  | 4  | 2  | 1  |

#### NOTE

While it is true that the value of 2<sup>15</sup> is 32768, bit 15 is never assigned that value. Instead, bit 15 is used as a sign bit, because the allowable range of integers is -32768 to +32767 inclusive. Whenever bit 15 is a 1-bit, it indicates that the rest of the binary word must be encoded or decoded as the two's complement of the actual number. See the following example for more details.

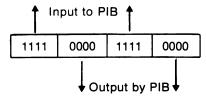

### Example 1. Converting A Binary Digit to an Integer (Direction Mask)

The port below is grouped into four sets of four lines each. The data direction alternates for each set:

Each input line is a 1-bit, so the binary value of the required integer is 1111000011110000. Since bit 15 is to be a 1, take the two's complement (invert all bits, add 1, and make the result negative). Note that the binary number can be encoded directly if the MSB is a zero.

1111 0000 1111 0000

$$(-)$$

0000 1111 0000 1111  $(+1)$

which encodes into the integer as follows:

$$-[1+2+4+8+256+512+1024+2048(+1)] = -3656$$

#### Example 2. Converting an Integer to a Binary Number

This conversion has many uses when you are working with the PIBLIB subroutines. It is used mainly when reading or writing a word at a port. Assume that RDWRD has just read the value of the word at a port to be -21846, and has placed that value into R%, the integer that was assigned to receive the returned value.

There are several options open to the programmer: first, the program might simply display the value, permitting it to be decoded manually (either by successive division by two, or by successive subtraction by powers of two, using the table above). The more efficient way, however, is to have the program itself do the decoding. Fluke BASIC has an easy way to do this conversion: the RAD\$ function.

The program:

```

100 PRINT "ENTER A DECIMAL NUMBER: "; \ INPUT R% 120 B$ = RAD$(R%, 2%) 130 BB$ = DUPL$("O", 16-LEN(B$)) + B$ 140 PRINT "Decimal Binary" 150 PRINT R%, BB$

```

would print the following if the number -21846 were entered:

To better understand how all this works, take a few moments to type in this short routine and plug a few numbers in.

#### **Event Interrupts**

The Parallel Interface Module can generate an interrupt to the CPU. The types and priorities of all interrupts are listed below.

| Priority | Interrupt Type                                   |

|----------|--------------------------------------------------|

| 1        | ON ERROR                                         |

| 1        | ON (CTRL)/C                                      |

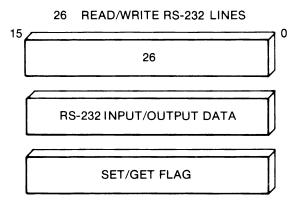

| 2        | ON #n (RS-232-C Channel)                         |

| 3        | ON KEY (the Touch-Sensitive Display)             |

| 4        | ON PORT                                          |

| 5        | ON PPORT (Parallel Interface Interrupt)          |

| 6        | ON SRQ (IEEE-488 Bus instrument service request) |

| 7        | ON PPOL (IEEE-488 Bus parallel poll)             |

| 8        | ON CLOCK                                         |

| 9        | ON INTERVAL Interrupts                           |