# CHAPTER 2 PRINCIPLES OF OPERATIONS

| 2.1  | General                   | 2-1   |

|------|---------------------------|-------|

| 2.2  | Power Supplies            | 2-4   |

| 2.3  | CPU Operations            | 2-29  |

| 2.4  | Clock Generator Circuit   | 2-50  |

| 2.5  | Jumper and Switch Setting | 2-57  |

| 2.6  | Reset                     | 2-63  |

| 2.7  | Keyboard                  |       |

| 2.8  | LCD Unit                  | 2-73  |

| 2.9  | A-D Converter             | 2-85  |

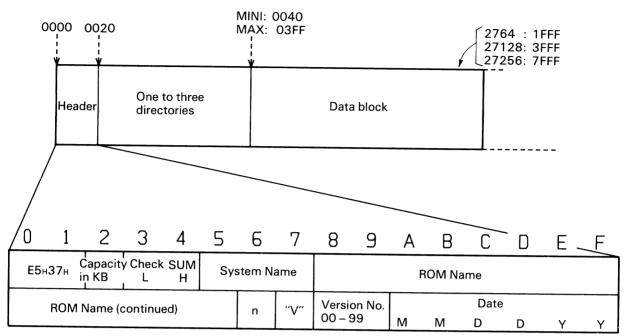

| 2.10 | ROM Capsule               | 2-96  |

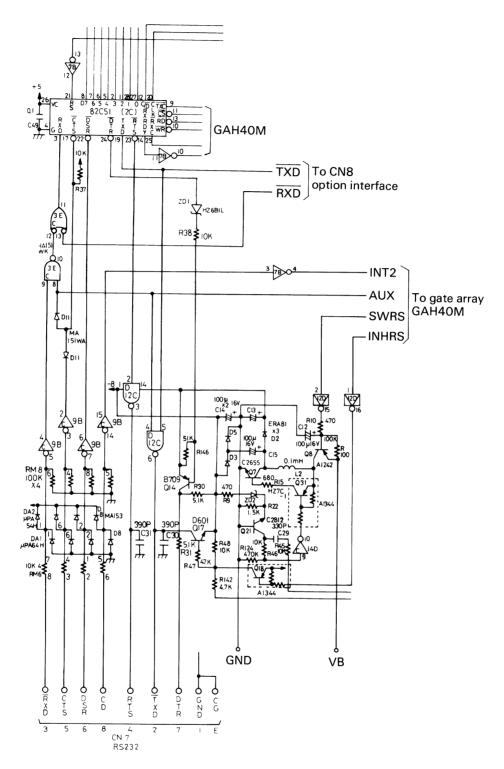

| 2.11 | RS-232C Interface         | 2-100 |

| 2.12 | Serial Interface          | 2-108 |

| 2.13 | Speaker Circuit           | 2-111 |

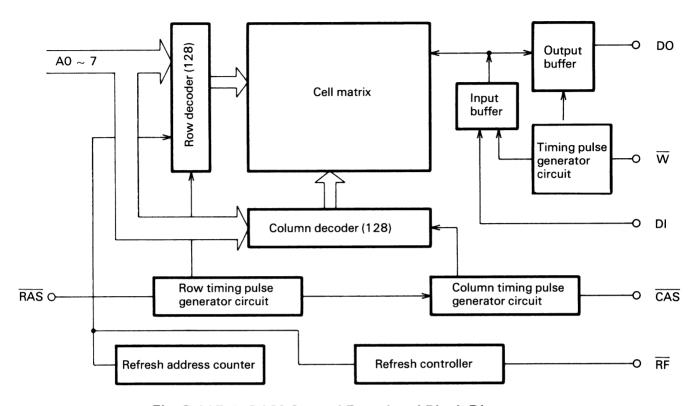

| 2.14 | Dynamic RAM               | 2-114 |

## 2.1 General

This chapter describes various functions of the main control board (called MAPLE board) which is the center of this computer. The microcassette drive and option units are described in Chapter 3. The MAPLE board uses a diversity of fully customized ICs (referred to as gate arrays throughout this manual), masked ROMs, and other chip elements (resistor, capacitor, transistor, and diode chips) which simplify component mounting. As many CMOS elements as possible have been used in order to lower power consumption. In addition, the computer provides the following features in order to control functions specific to battery powering:

- (1) Battery backup:

- Protects data in RAM.

- (2) Battery distribution (main and auxiliary battery power supplies): Ensures a more reliable battery backup.

- (3) Charge control:

- Prevents excess Ni-Cd battery charging.

- (4) Power distribution:

- Outputs the supply voltages only while the computer is in operation in order to minimize battery consumption.

- (5) Low voltage detection:

- Automatically changes the main battery to the auxiliary battery supply.

In addition, the computer is provided with a software automatic power-off feature which prevents the battery from being discharged out if the computer is inadvertently left on.

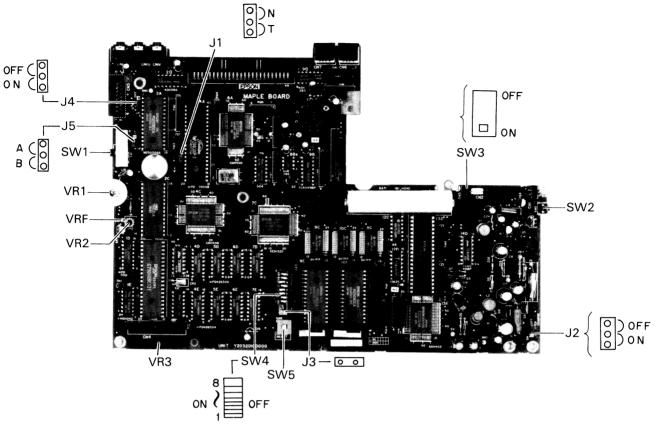

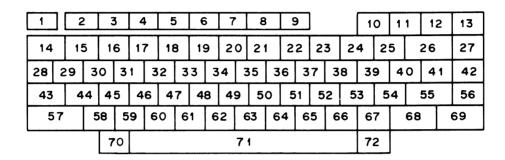

# 2.1.1 Major Components

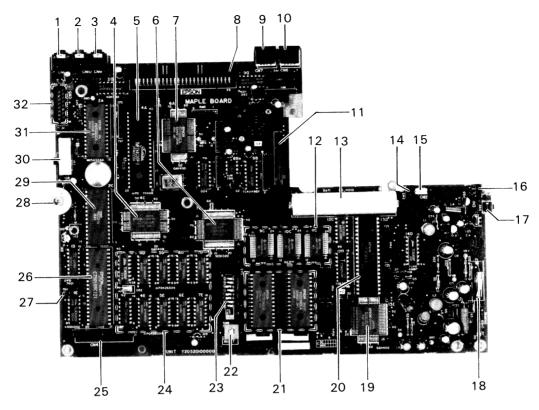

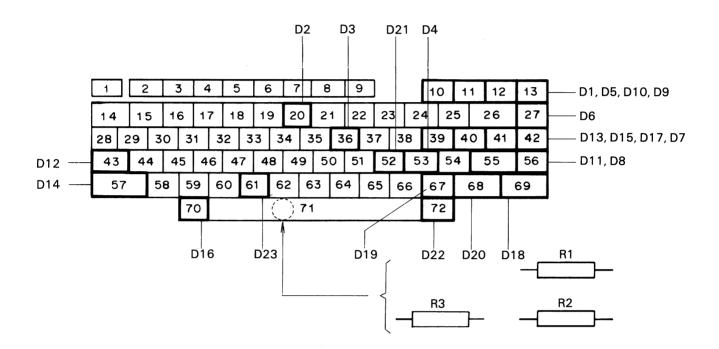

The MAPLE board has elements mounted on both the sides. A speaker and elements such as resistor packages, etc. are mounted on one side, while elements such as connectors, switches, and LSI chips, etc. are mounted on the opposite side as shown in Fig. 2-1. Table 2-1 lists major board elements together with a summary of their function.

Fig. 2-1 MAPLE Board Element Layout

**Table 2-1 MAPLE Board Major Components**

| No. | Name              | Function                               |

|-----|-------------------|----------------------------------------|

| 1   | CN11              | External speaker connector             |

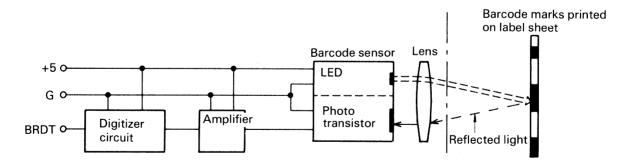

| 3   | CN9               | Barcode reader connector               |

| 5   | Main CPU          | Z80 CPU package                        |

| 7   | Gate array        | GAH40D package                         |

| 9   | CN7               | RS-232C interface connector            |

| 11  | CN3               | Microcassette interface con-<br>nector |

| 13  | Auxiliary battery | 90 mAH backup battery                  |

| 15  | CN2               | Main battery connector                 |

| 17  | SW2               | Reset switch                           |

| 19  | Gate array        | GAH40S package                         |

| 21  | ROM capsule       | (32 kB × 2)                            |

| 23  | SW4               | 8-position DIP switch                  |

| 25  | CN4               | Keyboard interface connector           |

| 27  | TH1               | Thermistor (for temperature sensing)   |

| 29  | Serial controller | 82C51 package                          |

| 31  | ROM               | 32kB ROM                               |

| No. | Name           | Function                                                 |

|-----|----------------|----------------------------------------------------------|

| 2   | CN10           | Analog signal input connector                            |

| 4   | Gate array     | GAH40M package                                           |

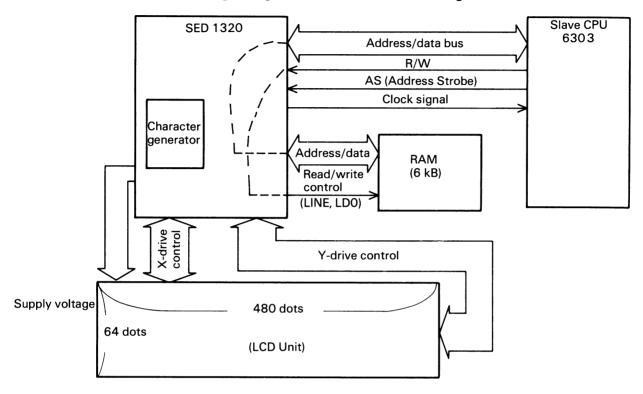

| 6   | LCD controller | SED 1320 package                                         |

| 8   | CN8            | Expansion interface connector                            |

| 10  | CN6            | Serial interface connector                               |

| 12  | V-RAM          | 6kB LCD RAM                                              |

| 14  | SW3            | Auxiliary battery control switch                         |

| 16  | CN1            | AC adaptor input (charge input) connector                |

| 18  | F1             | Fuse 3A                                                  |

| 20  | Sub-CPU        | 6303 CPU package                                         |

| 22  | SW5            | Initial reset switch                                     |

| 24  | D-RAM          | 64kB×8                                                   |

| 26  | 4-bit CPU      | 7508 CPU package                                         |

| 28  | VR1            | Speaker volume visual angle adjustment variable resistor |

| 30  | SW1            | Power switch                                             |

| 32  | CN5            | LCD interface                                            |

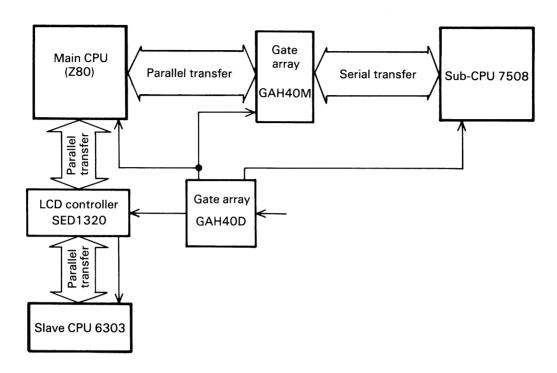

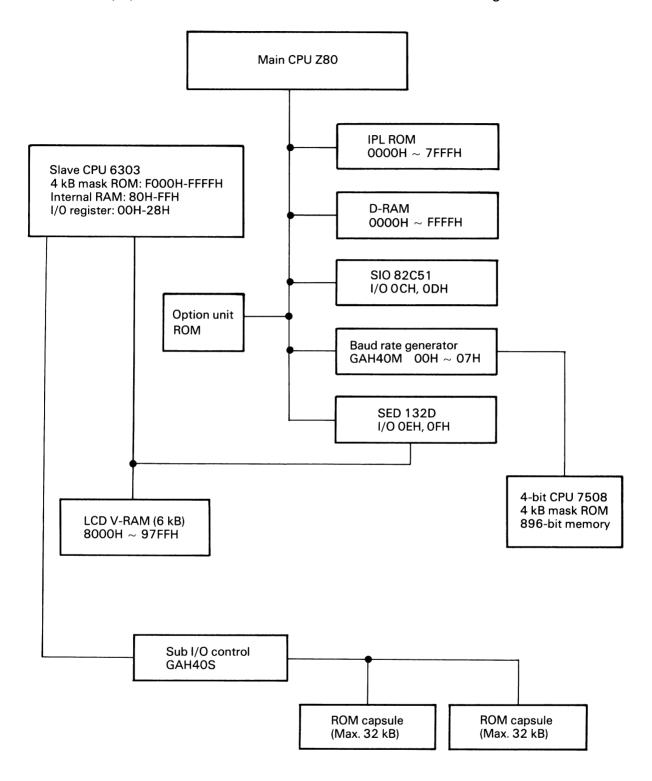

## 2.1.2 System Configuration

PX-8's main components include a main battery; the MAPLE (main) board, which along with control circuitry also contains an auxiliary battery; the LCD unit; the keyboard; and the microcassette drive assembly. The following block diagram demonstrates component configuration.

Fig. 2-2 Computer Configuration

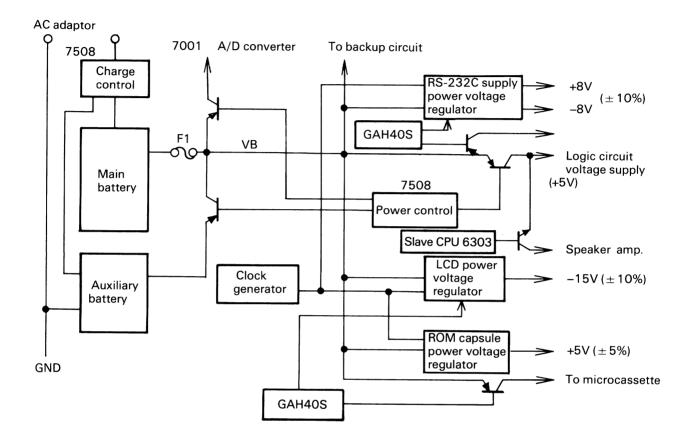

# 2.2 Power Supply

This computer operates with a rechargeable Ni-Cd battery and is provided with features for minimizing power consumption and controlling battery charge. The power supply is summarized in the following:

• Batteries: Two batteries; main and auxiliary, are used.

dition.

| Main battery |                   | Supplies a DC voltage of 4.8V and has a capacity of 1100 mAH. It  |  |  |

|--------------|-------------------|-------------------------------------------------------------------|--|--|

|              |                   | can power all the computer circuits; backing up the commercial as |  |  |

|              |                   | AC power when not used or unavailable. It also supplies power to  |  |  |

|              |                   | the attached option units.                                        |  |  |

|              | Auxiliary battery | Also supplies the DC 4.8V power. It has a capacity of 90 mAH and  |  |  |

|              |                   | backs up the main battery when in a low voltage (discharged) con- |  |  |

- Charging circuit: Supplies charging current to the main and auxiliary battery when an AC adaptor is connected. This circuit, which operates in either of two modes; normal and tricle (low current) charges, under the control of a sub-CPU 7508, controls the charging current.

- Voltage detection circuit: Monitors the voltage of the main battery using an internal AD converter. The result is processed by the sub-CPU 7508 to cause the circuit to provide two functions. One is low voltage detection which allows the computer, if it is operating, to display a warning message "CHARGE BATTERY" on the LCD screen, when the battery power (i.e., voltage) falls below a certain level. In addition, this function causes the computer to stop at an appropriate point in the operation in progress. The other function determines the normal charge restart timing; causing a switch from tricle to normal charge when AC adapter is connected.

- Backup circuit: Supplies the power required to maintain data in the RAMs when the power switch is off or the computer is not connected to the AC power line. It also serves to normally operate the circuits which monitor the battery voltage and detect whether power is on.

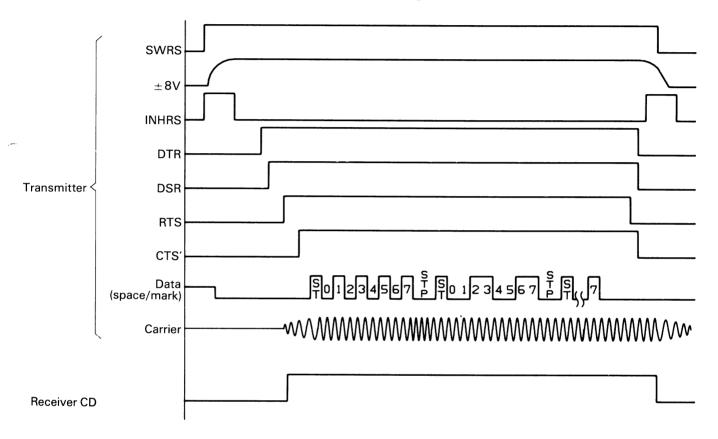

- ullet ±8V regulator: This voltage regulator supplies DC voltages of ±8V required for RS-232C operations. The voltages are generated from the battery voltage (VB) only when the RS-232C or serial interface is used.

- -15V regulator: Supplies a -15V DC voltage used for LCD display control. This voltage is generated from the battery voltage (VB) as long as power is on.

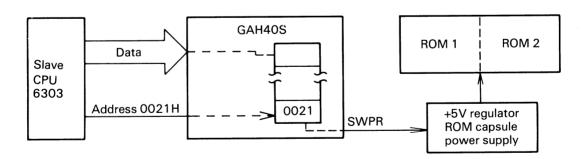

- 5V regulator: Supplies a +5V DC voltage used for the PROM capsule. This voltage is generated from the battery voltage (VB) only when the PROM is accessed. The regulator is provided in order to prevent a transient due to PROM access from directly affecting the VB line.

Other power circuits such as a switching circuit, which supplies the logic circuit power, are located on the MAPLE board, in addition to the above. Fig. 2-3 is a block diagram which summarizes the power supply circuits on the MAPLE board.

Fig. 2-3 Power Circuit Block Diagram

#### 2.2.1 Power On/Off Control

The power circuits are controlled by the 4-bit CPU 7508 which operates under a control program stored in a mask ROM built in it. If the CPU runs away due to some reason (battery power exhaustion for example), therefore, the power supplies are completely out of control. If this occurs, the AC adaptor should be connected to charge the batteries and then SW5 should be pressed to reset the CPU 7508.

#### 2.2.1.1 Power On

The computer is turned on by either of the following:

(1) Setting the POWER switch ON

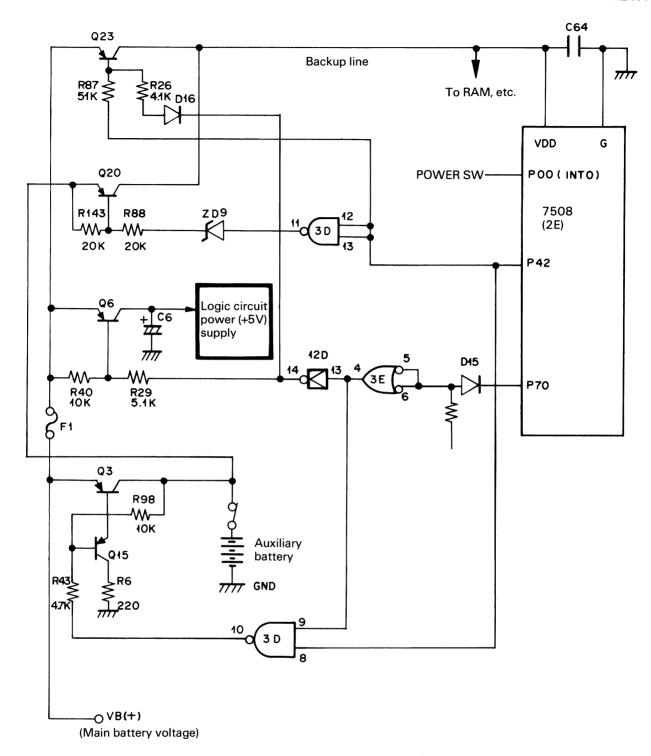

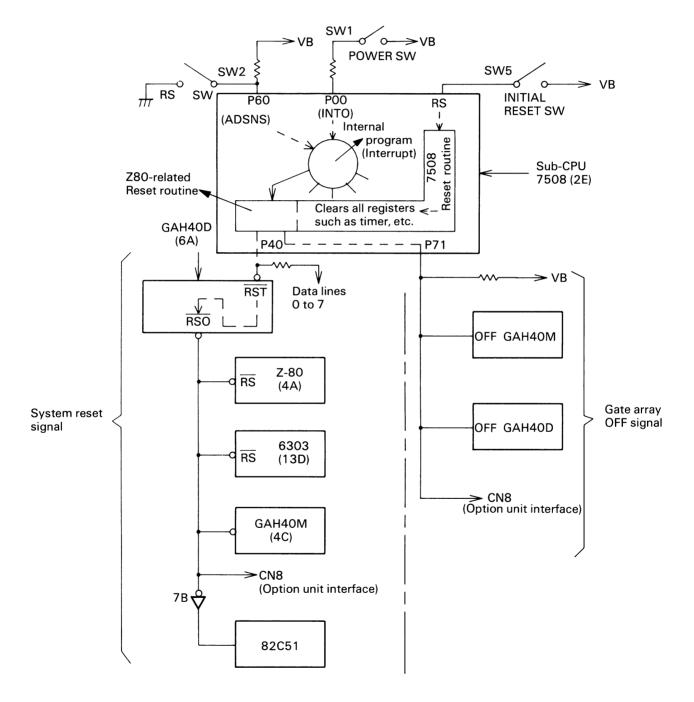

Setting the POWER switch ON causes pin 23 of CPU 7508 (INTO) to go high (see Fig. 2-4) which interrupts the control program for turning power on.

(2) Programmed power on

Power is automatically turned on regardless of the POWER switch setting when the time specified softwarewise with a "WAKE" command coincides with that of the clock built in CPU 7508.

#### 2.2.1.2 Power Off

Power is turned off by one of the following:

(1) POWER switch OFF

Turning the POWER switch OFF causes pin 23 of the 7508 CPU (INTO) to go low (see Fig. 2-4), interrupting the control program for turning power off.

(2) Low voltage detection

When a low VB line voltage is detected. The 7508 CPU interrupts the main CPU and current processing to be terminated at an appropriate point. At the same time, "CHARGE BATTERY" message display on the LCD screen for 30 seconds. The 7508 CPU then automatically turns power off if the POWER switch is at the ON position.

(3) Automatic (programmed) power off

The computer can be turned off by a software automatic power-off feature which uses the 7508 CPU's built in clock. This feature automatically turns power off when no I/O unit is used for a certain period of time even though the computer is in the key entry mode. Power off timing as follows:

• Default: 10 minutes

Specified: 1 to 255 minutes (specified by using the CONFIG command)

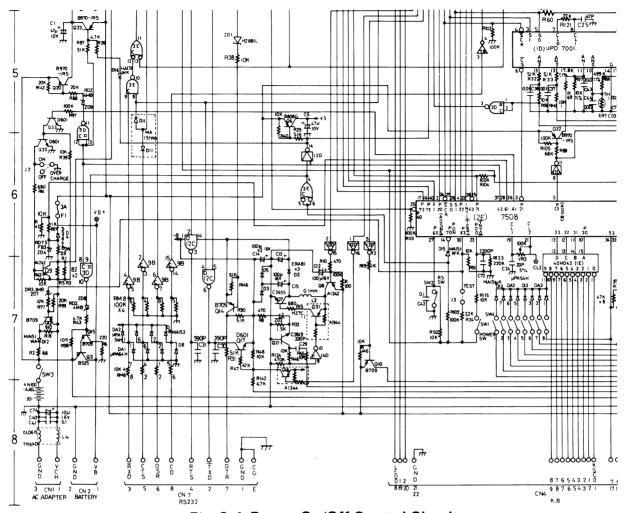

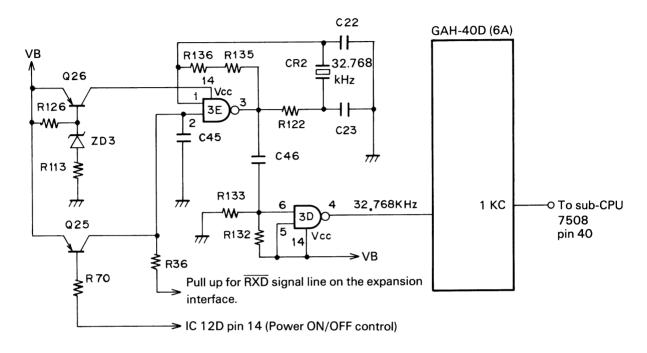

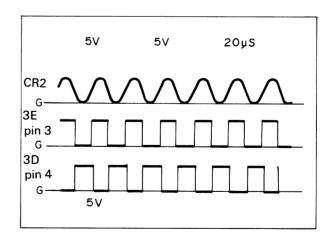

The following is a circuit diagram including the power on/off circuit:

Fig. 2-4 Power On/Off Control Circuit

- \* The power-off operation involves the following component functions:

- Microcasette tape drive head unloading

- Microcassette tape drive power off

- P-ROM cartridge power off

- RS-232C power off

- Barcode reader power off

- Speaker power off

It also controls the emergency power supply which allows the computer operation sequence in process to be completed and status information to be stored whenever the regular power supply is depleted.

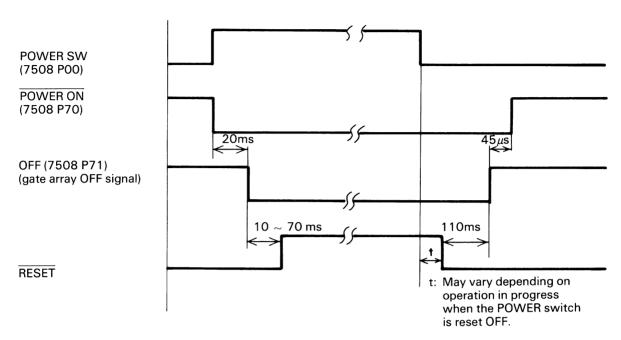

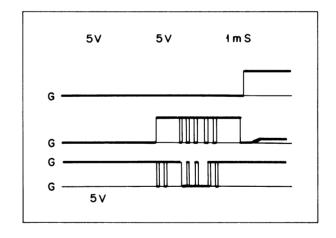

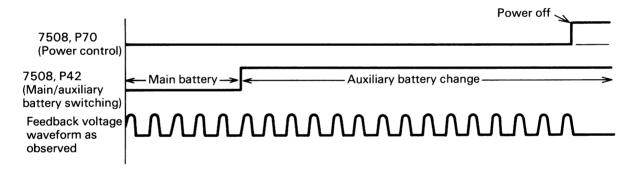

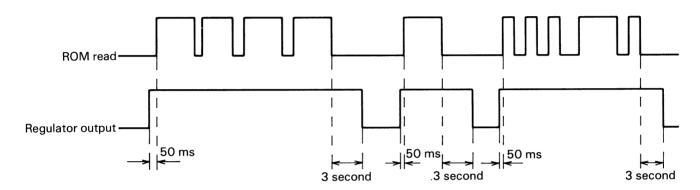

## 2.2.1.3 Power On/Off Timing

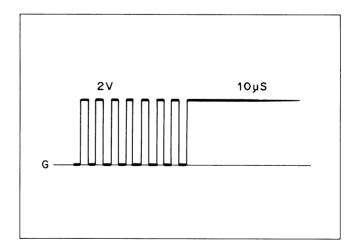

Power on/off has to be controlled by interrupting the sub-CPU 7508. Thus, either timing (the POWER ON or RESET signal) will be a little delayed as shown in Fig. 2-5

Fig. 2-5 Power On/Off Control Circuit

The time delay sequence illustrated in Fig. 2-5 above is only a sample time sequence. The power on/off operation permits any operation sequence in process, including the mechanical operation of an I/O unit (e.g., the microcassette) currently in progress, to be completed and the printer to be reinitialized before the power is off. The length of the illustrated time delay will vary according to which mechanical and/or logic sequence must be completed. The off signal is used to prevent a latch within the gate array.

# 2.2.1.4 Power On/Off Circuit Operations

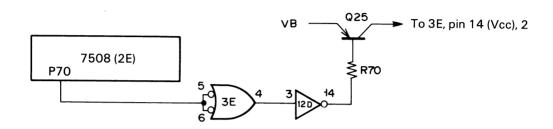

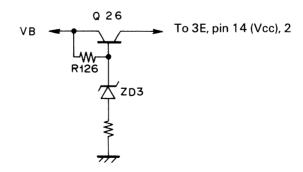

Fig. 2-6 shows the circuit. When the POWER switch is set ON or RESET off, or an automatic power on or off is input via software, the sub-CPU control program processes the power on or off as an interrupt using port 70 as follows:

• Power on: P70 of the sub-CPU 7508 going low causes the anode of D15 to go low, turning pin 4 of IC '3E' high. This in turn causes the output at pin 14 of the next inverter, 12D, to go low. This signal is fed to transistors Q6 and Q23 through resistors R29 and D16 respectively, turning them on. This causes the VB (+) voltage to be output at the collector of Q6, supplying the operation voltage (logic circuit voltage: VL) to the elements on the board. The transistor Q23 also supplies the VB(+) voltage to the battery-backed-up elements on the board. Thus, the board is ready to operate. Port 42 of the 7508 sub-CPU controls the backup for the auxiliary battery and can enable or disable conduction through transistor Q20. When port 42 output is high, the low level at pin 11 of IC 3D breaks down zener diode ZD9, holding Q20 in conduction. In this way the LCD drive voltage is insured, the message, "CHARGE BATTERY", will be displayed whenever the main battery output voltage falls to or below the low voltage limit.

- Power off: P70 of the sub-CPU going high, causes the output of pin 14 of inverter, 12D, to go high, turning Q6 off and thereby stopping the logic circuit voltage supply. Q23 is controlled by the sub-CPU, via P42, returning it to the normal backup operation.

- When the power-off request is an interrupt, generated when the POWER switch is turned OFF or low voltage is detected. When the power is turned Off and the power off request is comitted, the current operation has to be examined and a sequence excuted which assures that the operation in progress, including any I/O operation sequence, will be resumed without error when power is restored. The sequence allows all necessary processes such as the reinitialization of the I/O device (e.g., microcassette) in operation, a warning message display, etc. to be accomplished before the logic circuit voltage supply is actually removed.

- OFF signal: The OFF signal shown in Fig. 2-5 is controlled via P71 of sub-CPU 7508. This signal is emitted to gate arrays 6A and 4C, and the expansion interface CN8. It is intended to initialize the internal circuit of the gate arrays in order to prevent their outputs from being latched; it is a so called reset signal to the gate arrays and does not control power supply to the gate arrays.

The relationship between P70 and P42 of sub-CPU 7508 will be discussed in section 2.3, "Low Voltage Detection".

Fig. 2-6

# Note:

P70: POWER ON signal

High turns power off, and

Low turns power on.

P42: Main → auxiliary battery switching signal

High selects auxiliary battery, and

Low select main battery.

## 2.2.2 Charging Circuit

Two 4.8V, rechargeable, Ni-Cd batteries are connected to the MAPLE board. The main battery, which is housed the bottom case and can be replaced by loosening a single screw, has the larger capacity of 1100 mAH. Its charging circuit includes an overcharge protection circuit which protects the battery from overcharge by automatically discontinuing charge. The auxiliary battery, which is mounted on the MAPLE board, has a capacity of 90 mAH. A switch is inserted in both the charging circuit and backup line which can disable the backup by the auxiliary battery.

## 2.2.2.1 Main Battery Charging Circuit

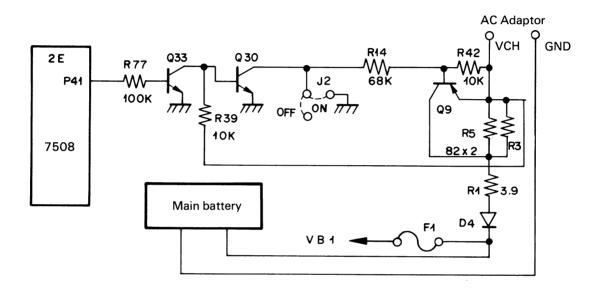

Fig. 2-7 Main Battery Charging Circuit

The charging circuit includes jumper A2 which allows two modes of charging:

When J2 is jumpered ...... No Overcharge Protection Control

Jumpering J2 causes the base of transistor Q9 to be always tied to ground, holding it in conduction. This effectively bypasses resistors R3 and R5, inserted in the charging circuit in series, and causes the charging current to be supplied to the battery through transistor Q9, current limiting resistor R1, and reverse-current preventing diode D4. This setting ecuses the battery to be continually charged as long as the AC adaptor is connected. Because of the low current limiting resistance in the mode of operation, the battery is highly liable to overcharge.

When J2 is open ...... Shipment Setting

• When J2 is open, the charge current bypassing transistor Q9 is controlled by the port 41 output of the 4-bit sub-CPU 7508. This CPU has a clock feature built in and maintains port 41 at the low level only for the <u>first eight hours</u> after it detects that the AC adaptor is connected, providing the same charging mode as when the jumper J2 is closed. With port 41 held low, transistor Q33 is cut off, leaving its collector at the high level (The collector is pulled up to the ac adaptor output through the resistor R39.) This maintains transistor Q30 in conduction; the collector is held at the low level, providing the same effect as if jumper J2 were closed.

• When eight hours have elapsed after the ac adaptor is connected to the AC line, port 41 of the 4-bit sub-CPU goes high, cutting off transistor Q9. This puts the circuit in the trickle charging state by inserting the resistors R3 and R5 (combined resistance, 41 ohms) in the charging path in series. The circuit constants are selected in this state so that the battery is substantially not harmed by overcharge, even if the battery is continually charged.

#### \*Reference

Following is the sub-CPU port operation for power control:

**Table 2-2 Sub-CPU Port Operation**

| Port      | Direction | Meaning                                   | Signal<br>level | Function                                                                                        |

|-----------|-----------|-------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------|

| P00       | IN        | Power switch                              | Low             | Power switch "OFF" interruption (H → L: —)                                                      |

| 1 100     | IIN       | interruption                              | High            | Power switch "ON" interruption (L → H:)                                                         |

| P23       | 0.1       | Main battery                              | Low             | Inactive                                                                                        |

| F23       | Out       | voltage detection                         | High            | Active Supply main battery voltage to A/D converter Supply operational voltage to A/D converter |

| <br>  P40 | out       | Reset                                     | Low             | Reset main CPU, slave CPU, etc.                                                                 |

| 140       |           |                                           | High            | Inactive                                                                                        |

| <br>  P41 | Out       | Recharging mode                           | Low             | Normal recharging mode                                                                          |

| ' - ' '   | Out       | control                                   | High            | Trikle recharging mode                                                                          |

| P42       | Out       | Battery back-up                           | Low             | Back-up with main battery                                                                       |

| 142       |           | control                                   | High            | Back-up with auxiliary battery                                                                  |

| P60       | In        | Reset switch                              | Low             | Active source input of "P40" and "OFF"                                                          |

| 100       |           |                                           | High            | Inactive                                                                                        |

| P61       | In        | AC adapter (re-                           | Low             | No AC adapter (non recharging condition)                                                        |

| 701       |           | charging opera-<br>tion) detect           | High            | Recharging condition (AC adapter is plugged)                                                    |

| P63       | Out       | Out Recharging mode for auxiliary battery | Low             | Normal recharging mode                                                                          |

| P63       |           |                                           | High            | Trikle recharging mode                                                                          |

| P70       | Out       | Out Powr ON                               | Low             | Power ON                                                                                        |

|           |           |                                           | High            | Power OFF                                                                                       |

| P71       | Out       | "OFF" signal for                          | Low             | Active (Initialize the '4C' '6A')                                                               |

| F/I       |           | gate array (6A, 4C)                       | High            | Inactive                                                                                        |

## 2.2.2.2 Main Battery Charging

In the following text, the functions of jumper J2 are summarized. Then, the actual main battery charging operations are described based in Fig. 2-8.

# (1) J2 jumper

The J2 jumper provides the following functions:

When closed: Disables the charging control; the battery is always charged as long as the AC

adaptor is connected.

When open: Enables the charging control; the battery is charged as follows when the AC

adaptor is connected, depending on whether power is on or off:

When power is on: The normal charge continues for the first 11 hours, and

then the trickle charge is used.

When power is off: The normal charge continues for the first eight hours, and

then the trickle charge is used.

\* With jumper 2 open and power off, the circuit remains in the trickle charge mode, after the normal charge, for the first eight hours. However, the circuit automatically returns to the normal charge mode whenever the battery voltage falls below 5V.

## (2) Charging Operations

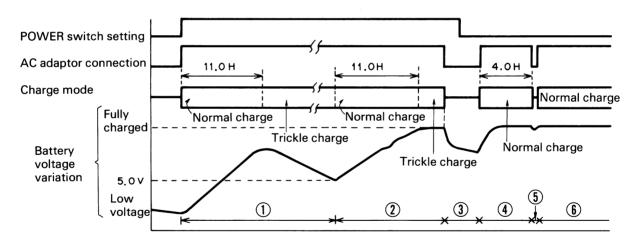

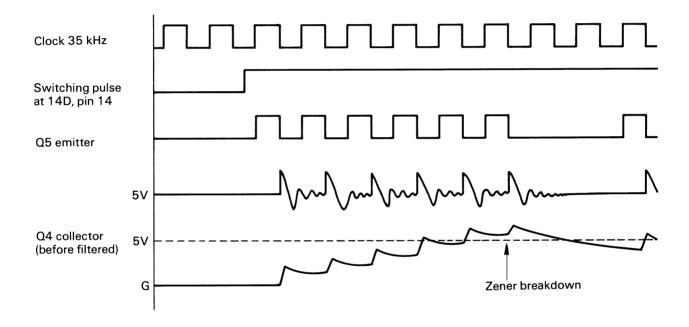

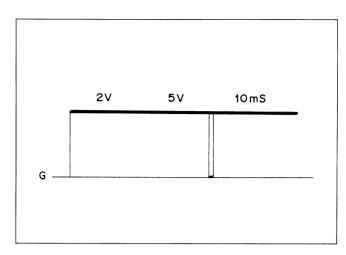

Fig. 2-8 is a timing diagram which illustrates the main battery charging operation when the charge control is in effect.

Fig. 2-8 Main Battery Charging Operation

Note: Battery voltages and charging currents:

Voltages:

When fully charged:

Approx. 5.4V

Low voltage:

Approx. 4.5 to 4.8V

Charging currents:

Main battery

Normal charge:

150 to 200 mA

Trickle charge:

40 mA

Auxiliary battery

Normal charge:

10 mA

Trickle charge:

1 mA

- Fig. 2-8 illustrates the main battery charging operation from a low voltage. The individual steps of the operation ① through ① are explained in detail in the following:

- ① Situation Low voltage is detected while the computer is used with the AC adaptor connected.

- The charging control is enable, and the battery is charged during normal computer use for aperiod of 11 hours. During that time, the battery may not be fully, charged depending on the particular use of the computer. After 11 hours, the charge mode changes to trickle charge in which the battery is charged at a current of approximately 40 mA. The figure shows a charging current of more than 40 mA, indicating that the battery is being discharged.

- ② Situation The battery voltage falls to 5.0V while the computer is used. Since the AC adaptor remains connected, the charge mode is switched back from trickle to normal charge. Sub-CPU 7508 always monitors the battery voltage using an A/D converter and, whenever it detects that the voltage has fallen to 5.0V or below, it automatically switches the mode through port 41. The circuit restores the same charging operation as ① above. The almost linear changes during the normal and trickle charges indicate that the charge and discharge currents remain almost constant during these durations.

- 3 Situation After the AC adapter is disconnected, the computer is used for a while, and then power is turned off.

- While the computer is used, the battery power decreases depending on how it is used. After power off, the battery power decreases for backing up the internal circuits.

- Situation The AC adaptor is connected while the power remains off. The eight-hour normal charge starts when the AC adaptor is connected. However, it is interrupted four hours after when the adaptor is disconnected. The battery is charged at the normal charge current during this interval regardless of the battery power.

- Situation The normal charge is interrupted by replacing the adaptor connection to another AC line outlet.

- Situation The adaptor is reconnected and the normal charge is resumed.

The eight-hour normal charge starts again when the AC adaptor is reconnected.

- Note 1: The main battery charging is controlled by detecting connection of the AC adaptor, regardless of the current residual battery power or the past charging operations. The 8- or 11-hour normal charge starts depending on whether power has been turned on or off when the adaptor is connected.

- Note 2: The battery may not be fully charged even though the adaptor is left connected for a long period of time. It is highly likely that the battery will remain below the full charge, especially when high power consuming operations are being performed while the battery charge is in process.

## When charging control is disabled

When the charging control feature is disabled, the battery is charged at the normal charge current as long as the AC adaptor is connected. Leaving the adaptor connected for a long time (overcharging the battery) may affect the life of the battery.

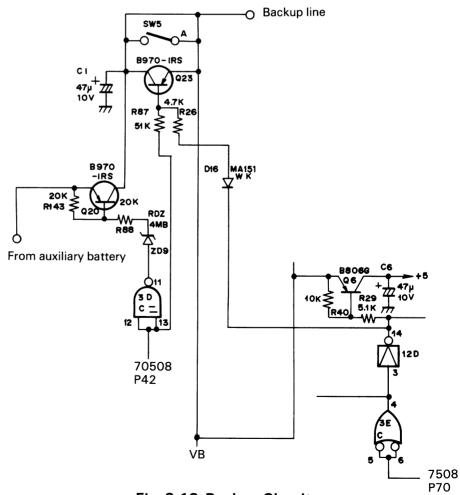

## 2.2.2.3 Auxiliary Battery Charging Circuit

As shown in Fig. 2-9, this circuit allows the user to select, via switch SW3, whether or not to enable charging and discharging (i.e., backup by the auxiliary battery). (SW3 is normally jumpered.)

When SW3 is jumpered, the battery is charged by one of the following three modes:

- When the AC adaptor is connected:

- The auxiliary battery is charged from VCH through R18.

- (2) The auxiliary battery is charged from VCH through Q13.

- When the computer is turned on:

- (3) The auxiliary battery is charged from the LCD power supply.

- Mode (1) is a trickle (low current) charge, which is enabled when the main battery voltage is 5.0V or below.

- Mode (2) is a normal charge which is enabled after low battery voltage (VB) condition is detected. When low voltage is detected, P63 of the sub-CPU 7508 is held low for 8.0 hours, forcing the normal (high current) charge.

The low level at P63 causes a potential dif-

0 7508 (P42) C 77 ZDS 20K 8709 MAI5 ЮK R98 68 R525 Auxiliary battery SW3 O 7508 (P63) 4N100 201 O LCD power supply 777 C74 DL0615 Main TR6Y-D batterv (from AC adaptor)

Fig. 2-9 Auxiliary Battery Charging Circuit

ference of approximately 6V (VCH voltage), which is AC adapter voltage, to appear across zener diode ZD7, breaking it down (ZD7 is a 3.3V zener diode). This lowers the base voltage of transistor Q13 below the collector voltage, putting the transistor in conduction, and providing the normal charging path from the VCH line through Q13, D12, and R2.

• Mode (3) constantly maintains the auxiliary battery in a fully charged state for emergency (the backup operation from the auxiliary voltage when low voltage is detected). Thus, the battery is continuously charged as long as the LCD power supply is available (whenever power is on) regardless of whether the ac adaptor is connected or not. See 2.2.5.2, LCD Voltage Regulator for details.

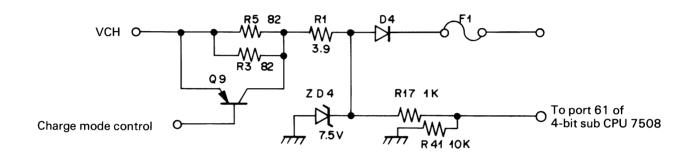

#### 2.2.2.4 Charging Timing Detection

The sub-CPU program is designed to control auxiliary battery charging from the AC adaptor using the built-in clock. Connection of the AC adaptor. Port 61 of the sub-CPU goes high whenever the AC adaptor is connected and the main battery is being charged. Since port 61 is connected to the anode of the diode D4 in the charging circuit through the resistor R17, the presence of the VCH voltage can be detected.

# 2.2.2.5 Protection Against Charging Voltage Supply Failure

An overvoltage detection circuit and a reverse-current blocking circuit are provided in order to protect the batteries and their charging circuits when any abnormal voltage occurs on the output of the ac adaptor; i.e., the charging voltage. The operations of the circuits are described in the following:

# (1) Protection against low voltage

The diode inserted in the charging circuit in series prevents reverse current if the charging voltage falls below the battery voltage.

## (2) Protection against overvoltage

If the voltage at the cathode of the zener diode (VCH) rises to +7.5V or above, the zener diode breaks down, and protect the overvoltage condition for VB+ line.

Fig. 2-10 Battery Protection Circuit

# 2.2.3 Low Voltage Detection

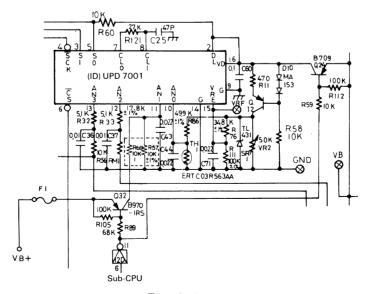

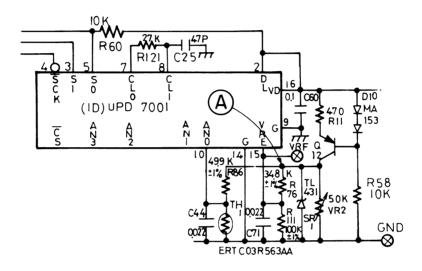

The 4-bit sub-CPU always monitors the battery voltage through an AD converter ( $\mu$ PD7001). When the battery voltage falls to +4.7V or below, the main battery is switched to the auxiliary battery.

## 2.2.3.1 Battery Voltage Detection Circuit

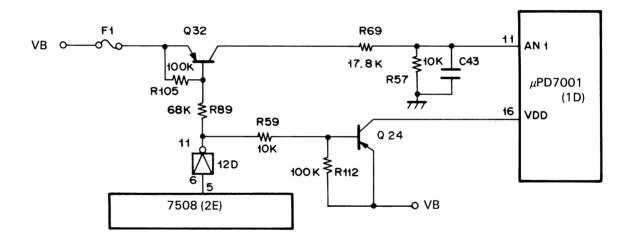

This circuit monitors the main battery voltage output through fuse F1 as follows:

• The built-in program of the 4-bit sub-CPU 7508 holds port 23 (pin 5) high. This causes IC 12D to hold its pin 11 low, putting transistors Q24 and Q32 in conduction. Q24 feeds the battery voltage (VB) to pin 16 of IC 1D (power terminal pin) to enable the AD converter μPD7001. Q32 feeds VB to the voltage divider (resistors R69 and R57). The divided voltage across R57 is fed to the AN 1 channel input of the AD converter which converts the input voltage to a 6-bit digital value representing a voltage value from 0V to 2.0V in a minimum increment of approximately 32 mV. When the digital value falls to D9H (approx. 1.7V) or below, the sub-CPU detects a low voltage condition.

Fig. 2-11 Battery Voltage Detection Circuit

The voltage supplied to the voltage divider circuit may be considered to be the same as the VB voltage. The current flowing through Q32 is so small that the voltage drop across the transistor is negligible. Thus, the divided voltage fed to the AD converter can be represented by the following expression:

$$V_{OUT} = \frac{VB(V) \cdot R57}{R69 + R57} = \frac{VB \cdot 10000}{27800}$$

The analog output (divider output) voltage equivalent to the digital value of D9H is given by multiplying the voltage represented by the least significant bit (SLB) (32 mV) by 217 (D9H). D9H is equivalent to a voltage of approximately 1.7V at the input terminal AN1, as shown below.

$$E = \frac{2}{256} \times 217 = 1.695 \text{ (V)}$$

where 256 voltage represented by LSB.

The VB voltage which causes the divided voltage to be detected to be a low voltage is approximately 4.7V as given by the following expression:

$$VB(x) = \frac{(R69 + R57)}{R57} \times \frac{2}{256} \times 217 \dots = 4.71 \text{ (V)}$$

**Note:** The above expressions do not take into account any errors such as the divider resistance errors, etc., and they actually include a total error factor of  $\pm 0.1$ V.

The above low voltage detection is performed regardless of whether power is on or off. After the after low voltage is detected, port 23 of the sub-CPU (pin 5) is back low to prevent further battery power consumption. While power is off, the voltage is **monitored every 10 seconds**.

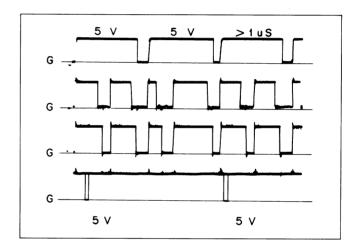

## 2.2.3.2 Voltage Sampling During Power Off

1. 12D, pin 11

1D power supply control

1D, pin 5SO (Serial Output)

3. 2E, pin 31D CS control

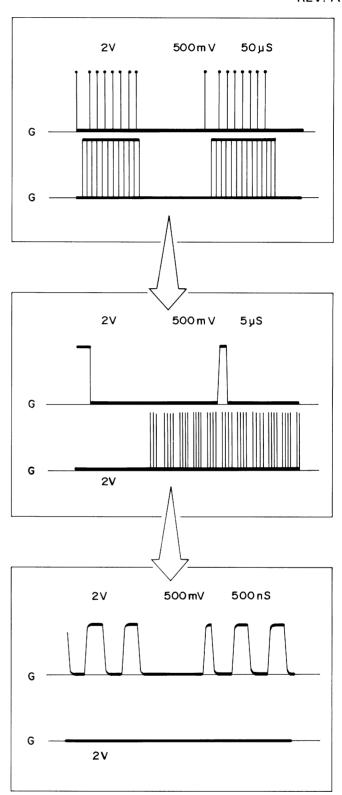

Fig. 2-12

The output at pin 11 of the IC 12D is controlled at port 23 of the 7508 (2E) sub-CPU. While power is off, it is held low for 8 ms every 10 seconds to power the IC  $\mu$ PD7001 (1D). Approximately 4 ms after the power supply to the IC, the  $\overline{\text{CS}}$  signal is input to it for channel selection. Once a channel is selected, the digital data of that channel is output to 1D, pin 5.

## 2.2.3.3 Circuit Operation After Low Voltage Detection

The 4-bit sub-CPU raises its port 42 (pin 37) high and controls the battery switching from main to auxiliary battery power as follows:

## When power is on

Since port 70 (POW ON) of the sub-CPU is low when power is on, the output at pin 4 of IC 3E is inverted high, holding pin 10 of the IC 3D low as inverted by the IC. The resistor R98 (100 kohms) and the zener diode ZD8 (4V) are connected in series across this pin and the anode of the auxiliary battery.

Normally, the auxiliary battery is fully charged, since it is always charged in the trickle charge mode, and has an output voltage of 4V or above. Thus, the zener diode intermittently breaks down. This in turn causes the transistors Q15 and Q3 to alternate conduction and cut-off. This operation intermittently continues until the auxiliary battery voltage reaches 4V (discharge final voltage). When Q3 starts conduction after the discharge final voltage is reached, a current flows from the auxiliary battery, which is connected to the emitter of Q3, to the collector; i.e., to the VB line, supplementing its power which is being supplied from the main battery. This operation ensures that the computer operation, such as microcassette rewind, etc., which is in progress when low voltage is detected, is normally completed.

• The high output from port 42 of the sub-CPU is also fed to the base of transistor Q20 to enable the backup voltage supply to the VB+ line from the auxiliary battery. The backup voltage supply ensures that the computer will continue to operate until an operation termination sequence is executed and the low voltage condition is detected. Subsequently, the "CHARGE BATTERY" message is displayed on the LCD panel.

#### When power is off

• When power is off, the high level of port 70 of the sub-CPU (POW ON) holds the output at pin 4 of the IC 3E low, disabling the AND logic consisting of pins 8, 9, and 10 of the IC 3D and holding the output at pin 10 high. This disables the power supply from the auxiliary battery to the VB line. However, the power supply to the backup line through the transistor Q23 is enabled.

## 2.2.4 Backup Circuit

The following elements are backed up by the battery voltage (VB) while power is off in order to protect data in the RAMs and maintain a clock feature, etc.

**Table 2-3 Battery Protected Component**

| Location           | Element name                     | Function                                                                                                                                |

|--------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 4D ~ 7D<br>4E ~ 7E | RAM                              | Main RAM (dynamic)                                                                                                                      |

| 9C ~ 11C           | V-RAM                            | LCD display RAM (static)                                                                                                                |

| 2E                 | 4-bit sub-CPU                    | Power control, keyboard scanning                                                                                                        |

| 3D                 | Gate                             | Backup line control                                                                                                                     |

| 3E                 | Gate                             | Power-on signal gate                                                                                                                    |

| 4C, 6A<br>*1D      | Gate array<br>8-bit AD converter | Interrupt and clock control, etc. Battery voltage detection and temperature change detection (for RAM refresh rate determination), etc. |

\* The operating voltage is supplied for 8 ms every 10 seconds.

The backup circuit is shown in Fig. 2-13. As can be seen, the circuit is normally backed up from the VB line via the transistor Q23, regardless of whether the computer is operating or not. It is backed up from the auxiliary battery when low voltage is detected.

For details of the circuit operations, refer to the descriptions on the power on/off circuit.

Fig. 2-13 Backup Circuit

## 2.2.5 DC Voltage Regulators

The MAPLE board is powered by the main or auxiliary +5V Ni-Cd battery. For circuits such as an I/O control section which requires different operating voltages and any special section which requires a larger current, however, voltage regulators are used to convert the battery voltage to the required voltages and prevent the circuit operation from being affected from a voltage drop due to use of large amount of current. The internally used voltage regulators are summarized below:

(1) +5V regulator

Purpose: ROM capsule power source.

Control: Enabled when the ROM capsule is reread.

Output voltage:

(2) LCD drive source regulator

Purpose: LCD drive power source.

Control: Always enabled.

Output voltage: -15V (The LCD is actually driven by a voltage of 20V obtained using

the potential difference from the +5V supply.)

(3) RS-232C level source regulator

Purpose: Sources for the RS-232C levels of  $\pm$  8V.

Control: Enabled only when the RS-232C or serial interface is operated.

Output voltage:  $\pm 8V$

The individual regulators are detailed in the following:

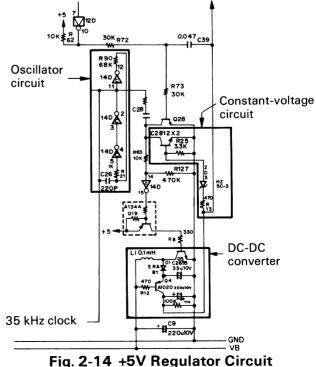

## 2.2.5.1 +5V Regulator

This regulator supplies power to the ROM capsule. When accessed, the ROM generates such a large transient current that, if it were directly powered by the battery, a momentary low voltage condition would occur due to a voltage drop along the power line, precluding normal operation.

To prevent this, the regulator is provided as a power buffer. The circuit operation is detailed as

follows (Refer to Fig. 2-14):

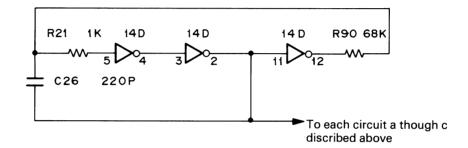

- The SWPR signal is low when power is off and is inverted high at pin 10 of the IC 12D. This signal maintains transistor Q28 in conduction, holding the collector low. Thus, the switching signal fed from pin 2 of IC 14D does not appear at the lower terminal of the capacitor C28 (collector of Q28) and the transistor Q19 is cut off, generating no output voltage.

- When power is off, transistor Q28 is cut off by the high level of the SWPR signal, and a clock signal of approximately 35 kHz is fed to pin 14 of IC 24D. This causes a pulse signal at the collector of the transistor Q19, which repeats, switching transistor Q5 on and off.

The collector of Q5 is connected to the VB line (+5V) through inductance L1 and the emitter is grounded. When the transistor repeats switching on and off, therefore, a voltage as shown in Fig. 2-15 appears at the collector. This voltage is filtered by the electrolytic capacitor, C3, through the diode D1 to a voltage that exceeds VB. This results in a potential difference across the emitter, and base of the transistor Q4, which causes the transistor to conduct, outputting a DC voltage of approximately 7V at its collector.

Because this output is connected to the constant-voltage circuit, consisting of the resistors R13 and R25, and the zener diode ZD5, the actual output voltage is fixed at +5V by the 5V breakdown voltage of the zener diode. When the Q4 output voltage rises above +5V, ZD5 breaks down at +5V, putting transistor Q22 in conduction, which forces the switching signal to ground level. The output voltage is always maintained at +5V by disabling the switching of Q5. Variation of load is handled by the relatively large capacitance of capacitor C8 (220  $\mu$ F), connected at the collector of Q4.

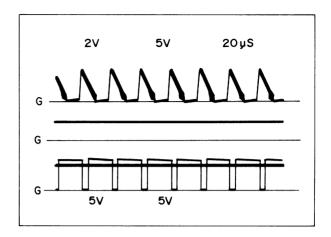

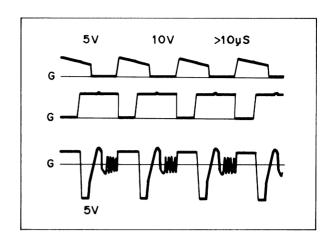

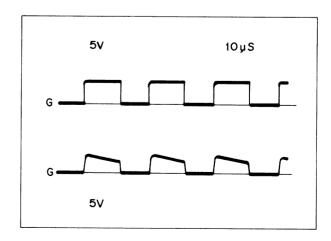

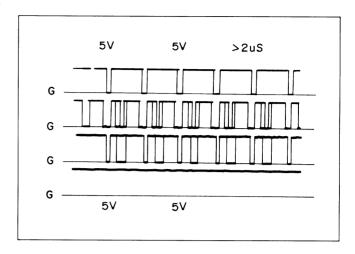

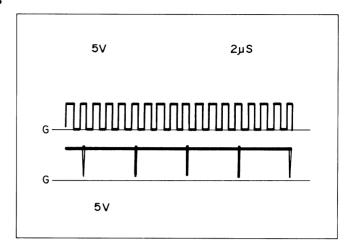

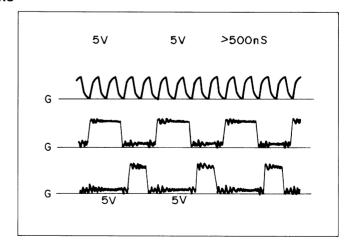

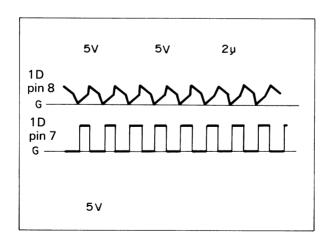

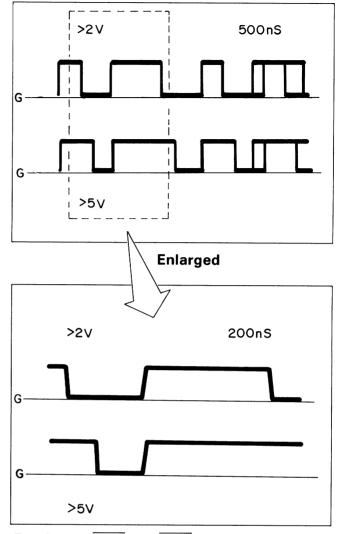

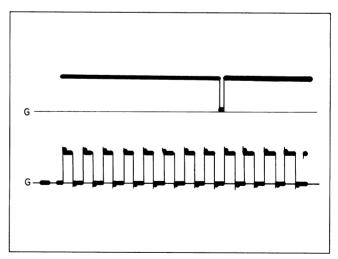

Fig. 2-15 +5V Regulator Voltages

Major actual voltage waveforms are shown below.

- (1) Top Test point: IC 14D, pin 14

- (2) Center Test point: IC 14D, pin 15

- (3) Bottom Test point: Diode D1, cathode

Fig. 2-16 Major Voltage Waveforms In +5V Regulator Circuit

Details of the above waveforms are enlarged below for clarity.

Fig. 2-17 Major Voltage Waveforms Enlarged

Though it looks as if Q5 continued to oscillate due to false images in the above photograph, it actually switches once almost every several switching clock pulses. This ratio varies depending on load.

## 2.2.5.2 LCD Drive Source Regulator

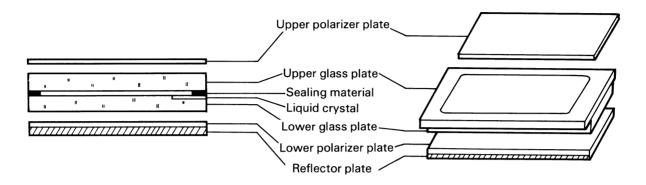

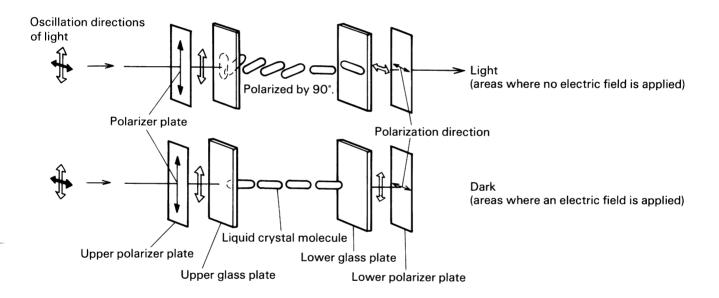

Two voltage supplies are required to drive the LCD display;

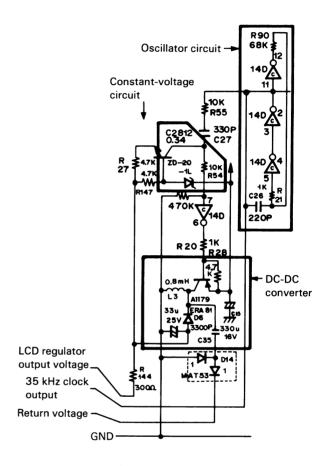

+5V is required for the logic circuit, and 20V is required for the X-Y drivers. A total potential difference of 20V is obtained by subtracting the –15V output voltage of this regulator from the +5V of the logic circuit power supply. Fig. 2-18 shows the regulator circuit.

## **Circuit Operation**

The oscillator circuit generates a clock of approximately 35 kHz when the POWER switch is turned on. This clock is fed to pin 7 of the IC 14D through R55, C27, and R54. The inverted output at pin 6 is input to the base of the transistor Q29 through R20, switching it on and off.

The emitter of Q29 is connected to the +5V logic circuit power supply and the collector is connected to ground through inductance L3. As the transistor is switched on and off by the clock signal, a voltage, as shown in Fig. 2-20, which is the counter electromotive force across L3, appears at the collector of Q29. While the collector voltage swings negative, a current flows in through diode D6, generating a negative voltage at the negative side of capacitor C17. This output is used as the LCD drive source voltage. It is also fed to the constant voltage circuit which connects the LCD drive voltage to the +5V logic circuit line through the resistor R147 and the zener diode ZD20. The zener diode has a breakdown voltage of 20V. Thus, when the output voltage rises to -15V or

Fig. 2-18 LCD Drive Source Regulator Circuit

above, the zener diode breaks down, raising the base of the transistor Q34 to the high level of +5V. This puts the transistor in conduction and its collector is driven negative, disabling the clock signal to Q29. This stops switching of Q29 and thereby lowers the output voltage. This state is maintained until the zener breakdown comes to an end. At that time, Q29 switches again. The circuit repeats this operation to produce a stable voltage of -15V.

The signal generated at the collector of Q29 is fed to the diode D14 through the capacitor C35. The negative component of the signal is removed by a current supply from ground through diode D14, while the positive voltage is fed back to the auxiliary battery through D14.

The diode, inserted across the signal line and ground, clamps the signal to the ground level, eliminating the negative component. While the positive component is fed back to the auxiliary battery via the other diode D14.

Fig. 2-19 Feedback Circuit

Fig. 2-19 is the feedback circuit redrawn for clarification. This circuit provides the charging path to the auxiliary battery while power is on.

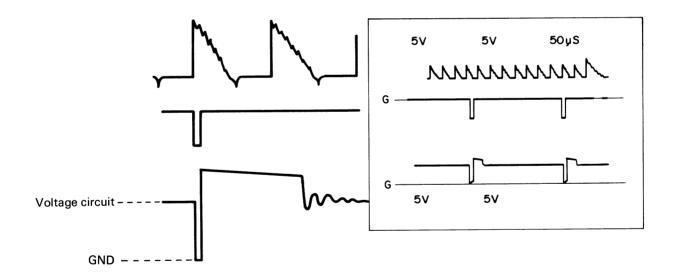

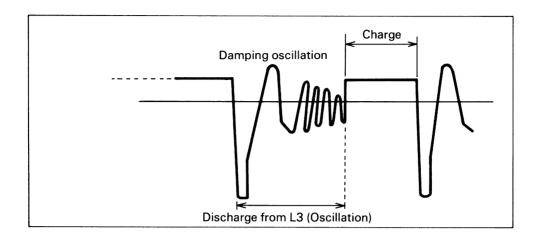

Fig. 2-20 Major Voltages of LCD Drive Power Regulator Circuit

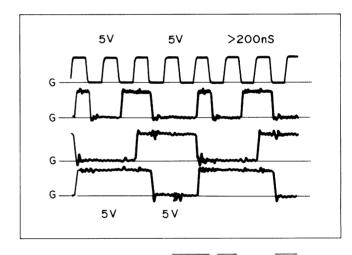

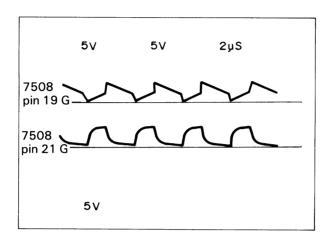

Fig. 2-21 is a photograph of the major voltage waveforms.

(Top) Measured at IC 14D, pin 7 (Center) Measured at IC 14D, pin 6 (Bottom) Measured at diode, anode

Fig. 2-21 Major Voltage Waveforms of LCD

Drive Power Regulator Circuit

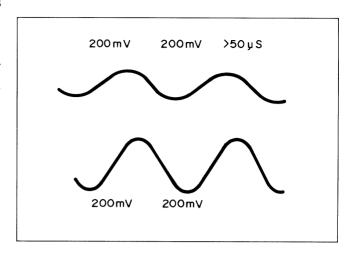

\* The detailed voltage waveform at the anode of D6, shown below, illustrates an oscillation which occurs during charge/discharge from/to the inductance L3.

Fig. 2-22 Details of L3 Discharge and Charge Cycle

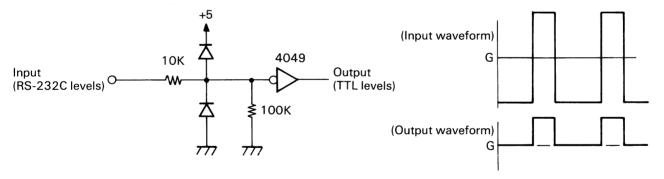

## 2.2.5.3 RS-232C Regulator

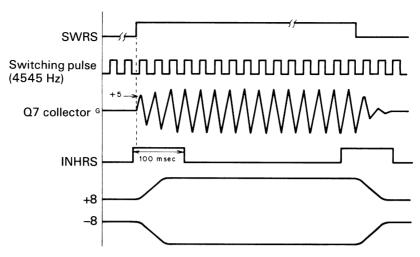

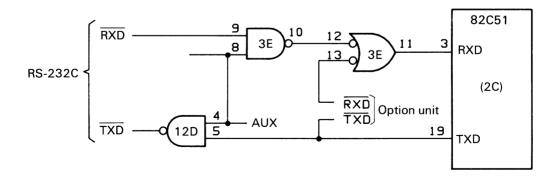

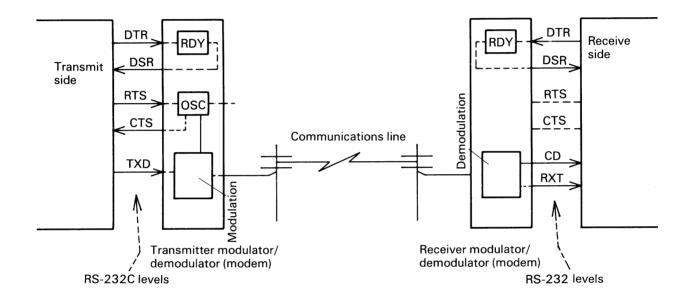

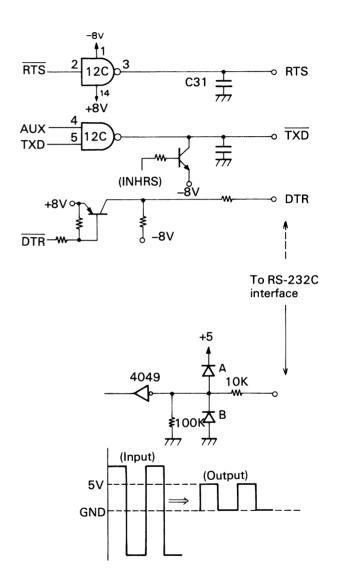

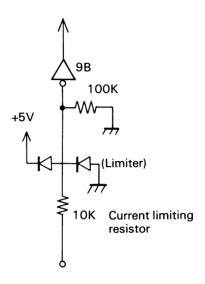

This regulator is also a DC-DC converter, which is enabled only when the RS-232C or the serial interface is used. The circuit includes a control feature which prevents its output voltage from being used for data transmission during a certain period of the rising time until the voltage is sufficiently stable to be used for the RS-232C levels. IC 4C performs this control function.

## Circuit Operation

IC 4C initially outputs a high signal at pin 26 (SWRS) and a low signal at pin 27 (INHRS). The SWRS signal is inverted by IC 12D and fed to the base of the transistor Q8, turning it on. This causes the battery voltage (VB, +5V) to be output at the collector of the transistor. The INHRS signal is inverted high by 12D and then input to the base transistor Q18, cutting the transistor off. Q17 is also cut off, leaving the transmission line (TXD) floating.

A pulse signal of approximately 35 kHz, generated by a CR oscillator circuit, is supplied to pin 9 of IC 14D through R45, C29, and R46. The inverted output is fed to the base of transistor Q31, switching it on and off. This causes transistor Q17 to also start switching, thus repeating a discharge/charge from or to the inductance L2. This discharge and charge voltage is half-wave rectified by the diode D2, and the positive output voltage is filtered by capacitor C13 to produce a DC voltage of +8V. –8V is generated at the negative pole of capacitor C14 by the negative component charge to capacitor C15 and a negative voltage swing at the anode of diode D3 due to the charge.

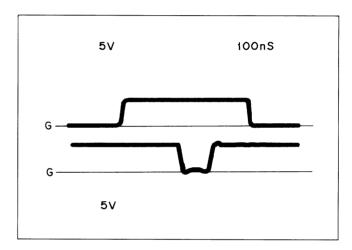

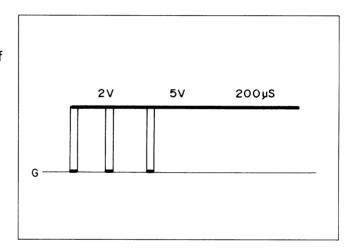

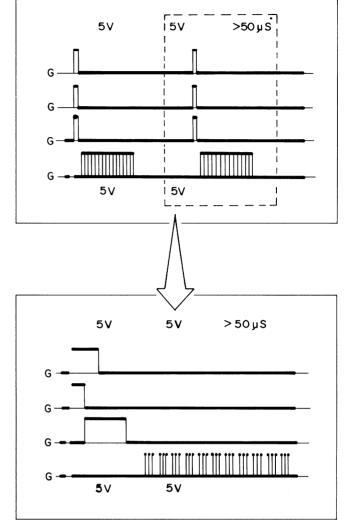

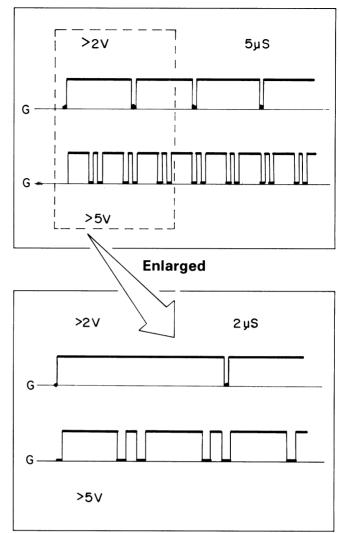

Fig. 2-23 shows the timing relationship among the voltages discussed above.

Fig. 2-23 RS-232C Power Regulator Circuit Operation Timing Diagram

The INHRS signal controls the pull-up operation (–8V) for the TXD line. It prevents irregular output voltages from reaching the TXD line. After power is turned on, if the SWRS signal has been activated, the INHRS signal is maintained low for approximately 100 ms, preventing the TXD signal line from being pulled up to unstable voltages. After power is turned off, the INHRS signal is again maintained low for approximately 100 ms in order to prevent a pull-up to unstable voltages.

# Voltage Stabilizer Circuit

The switching of transistor Q31 is controlled by a feedback from the –8V output of this DC-DC converter to the switching circuit to generate a constant output voltage.

When the -8V line voltage is lower, no potential difference is generated across the base (ground) and emitter of the transistor Q21; it is maintained in the off state because the zener diode ZD2 does not break down, and the switching circuit is not affected. When voltage rises to 7V or above, however, ZD2 breaks down at its zener voltage, generating a potential difference across the base and eimitter of Q21, turning it on. In this state, the collector is held at a negative level regardless of the switching pulse. Transistor Q31 is cut off and stops switching, lowering the output potential. This causes the breakdown of ZD2 and allows the switching to be resumed. The sequence of these circuit operations is repeated to provide two stable voltage levels of  $\pm$  8V.

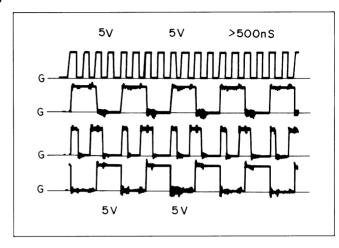

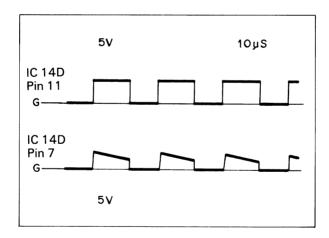

The RS-232C power regulator switching signal is shown in Fig. 2-24.

- (1) Top: Original clock signal Measured at IC 14D, pin 11.

- (2) Bottom: Input to RS Measured at IC 14D, pin 7.

Fig. 2-24

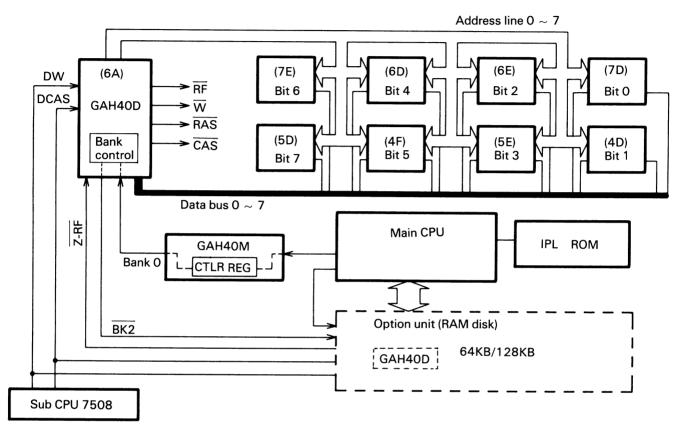

# 2.3 CPU Operations

Control of memory, I/O, and various other functions is distributed among the three COMS CPUs on the MAPLE board.

## (1) Main CPU (Z80).....2.45 MHz

The main CPU provides overall control of circuit operations using the external 32 kB ROM (2A). Its major control functions are:

- Expand interface (CN8) control

- RS-232C interface operation control via a serial controller

- 64 kB dynamic RAM read/write and refresh operation control via a gate array (GAH40D)

- RS-232C interface control via a serial controller (82C51)

- RS-232C clock supply via a baud rate generator (GAH40M)

# (2) Sub-CPU (7508).....200 kHz

The sub-CPU provides the following circuit operation control functions independent of the main CPU using the internal 4 kB masked ROM:

- Command exchange with the main CPU via a gate array (GAH40M)

- Power on/off control

- Change mode (normal or trickle) control

- Keyboard data entry check

- DIP switch setting read

- A-D converter enabling/disabling control

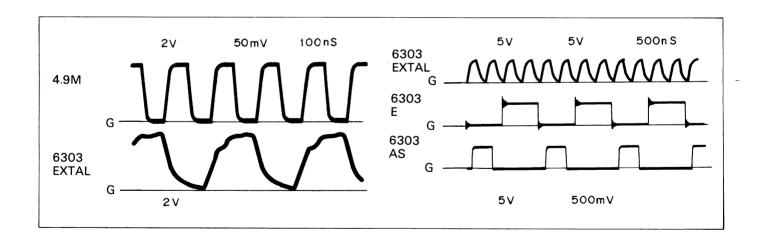

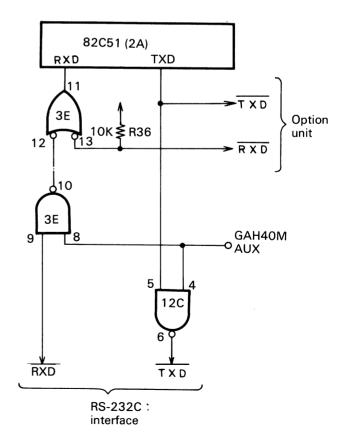

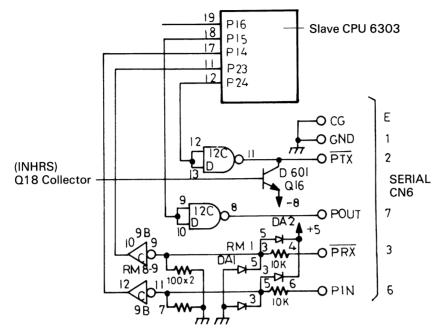

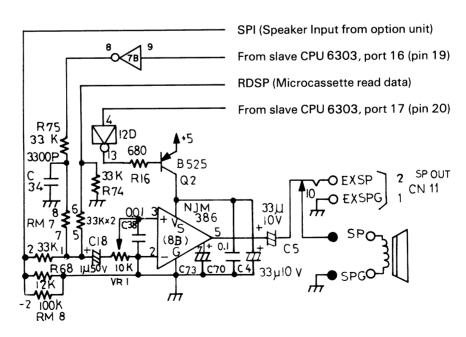

#### (3) Slave CPU (6303).....614 kHz

The 6303 provides the following control functions independent of the main CPU, using the internal 4 kB masked ROM:

- Command exchange with the main CPU via the LCD controller (SED1320)

- Microcassette control via a gate array (GAH40S)

- High speed serial interface control

- Speaker output control

- LCD display control via the LCD controller (SED1320)

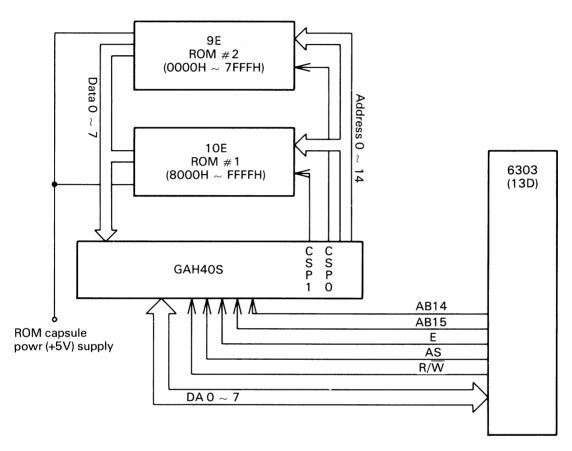

- ROM capsule read control via a gate array (GAH40S)

# 2.3.1 Handshaking Between Main CPU and Sub-CPUs

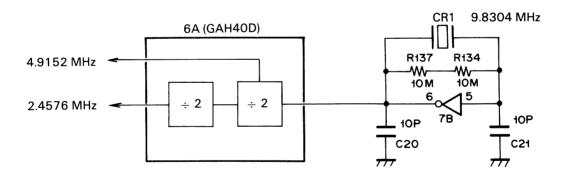

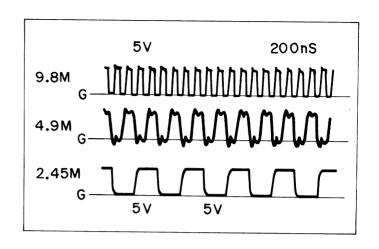

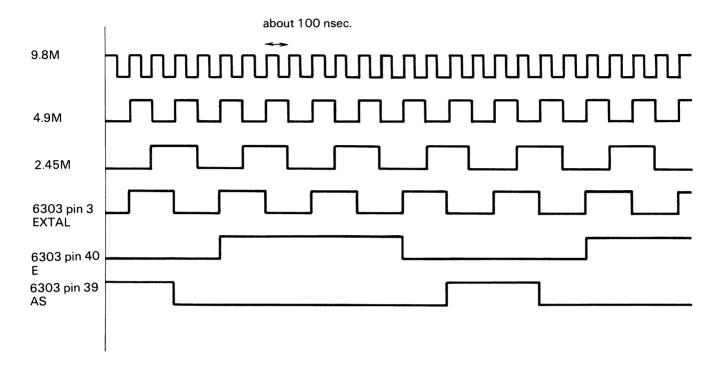

The three CPUs operate using a clock supplied from a gate array (GAH40D), which has a built-in frequency divider circuit. Data and commands are exchanged between the main CPU and the two sub-CPUs as follow:

Data exchange between Z80 and 6303: Handshaking is accomplished via the LCD controller. Data exchange between Z80 and 7508: Handshaking is accomplished via the gate array GAH40M.

Fig. 2-25 Data/Command Exchange Between Main CPU and Sub-CPUs

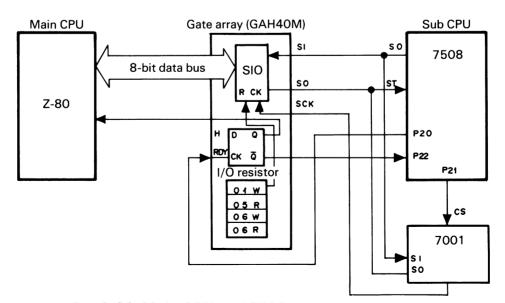

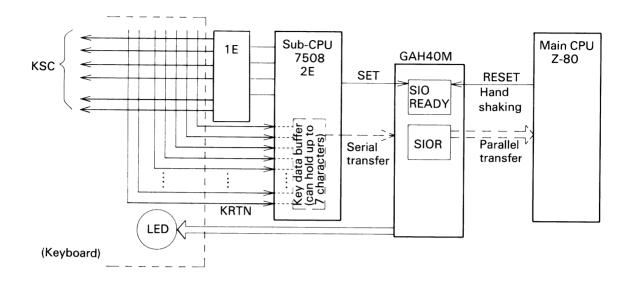

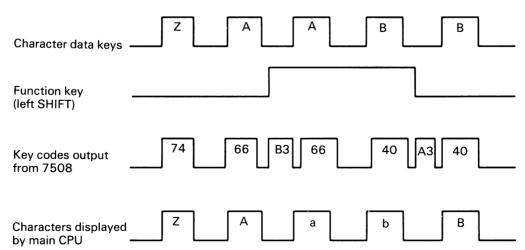

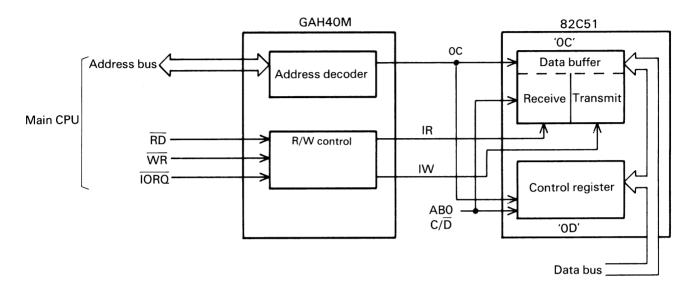

# 2.3.1.1 Data/Command Exchange Between Main CPU and Sub-CPU 7508 via GAH40M

Commands are transferred in parallell between the main CPU and gate array and serially between the gate array and sub-CPU 7508. Handshaking among the CPUs is performed via the read/write control on the serial/parallel conversion register in the gate array. Fig. 2-26 illustrates this control.

Fig. 2-26 Main CPU and 7508 Handshaking Control

Handshaking is accomplished using a flipflop (FF) within the gate array. The FF signals, when it is set, that the main CPU may access the serial I/O (SIO) register in the gate array; the sub-CPU is issued an interrupt, when it is reset, that a command has been written to the SIO from the main CPU, and is available for access by the sub-CPU.

- Operation sequence between main CPU and gate array.

- 1. Main CPU reads the I/O address 05H (status register) and checks the state of bit 2 (the FF). The bit indicates, when it is on, that the main CPU may access SIO.

- 2. Main CPU reads or writes SIO (I/O address 06H).

- 3. Main CPU writes bit 1 of the command register (I/O address 01H) and sets FF.

- Operation sequence between the sub-CPU and gate array.

- 1. Sub-CPU waits until its port 22 goes high (this occurs when FF is reset by the main CPU), indicating that main CPU has stored a command in SIO.

- 2. Sub-CPU issues the shift clock (SCK) and reads in the command from SIO one bit at a time and performs the specified processing.

- 3. Sub-CPU activates its port 22 to set the FF-setting. The FF informs the main CPU that the command has been received and the SIO is now available for access by the main CPU.

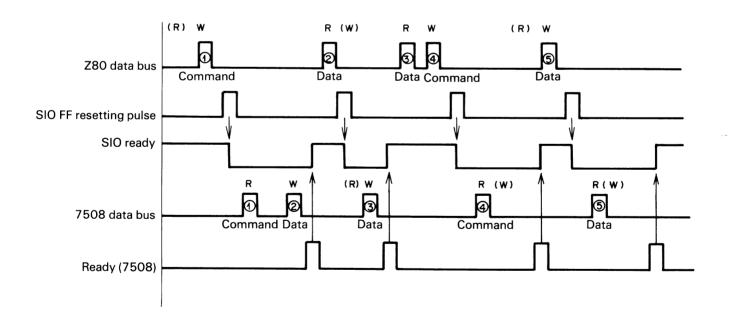

- Fig. 2-27 illustrates the interfacing operation between the main CPU and sub-CPU 7508 via the gate array.

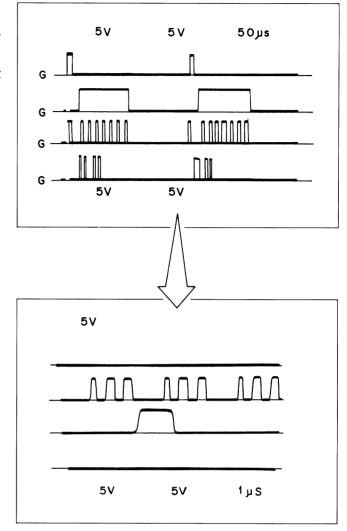

Fig. 2-27 Main CPU and Sub-CPU Interfacing Signal Timing

As can be learned from the figure, the handshake is accomplished via the SIO READY signal as follows:

When SIO READY is set : Z80  $\leftarrow \rightarrow$  GAH40M When SIO READY is reset : 7508  $\leftarrow \rightarrow$  GAH40M

The SIO READY signal is set and reset by the following signals:

SIO READY is reset when READY FF is reset by bit 0 of Z80 I/O address 01.

SIO READY is set by 7508 port 22.

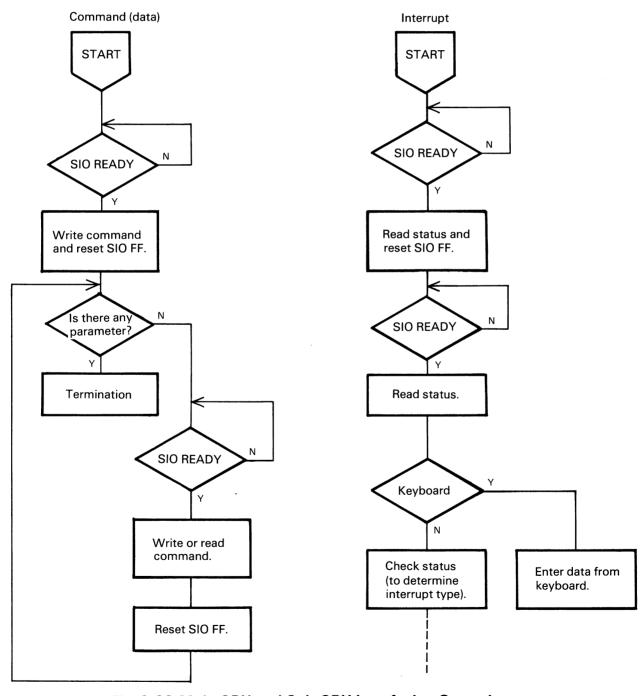

The SIO READY signal is set and reset either by a command (data) or interrupt. The operations are illustrated by Fig. 2-28

Fig. 2-28 Main CPU and Sub-CPU Interfacing Operations

## (Serial Data/Command Transfer)

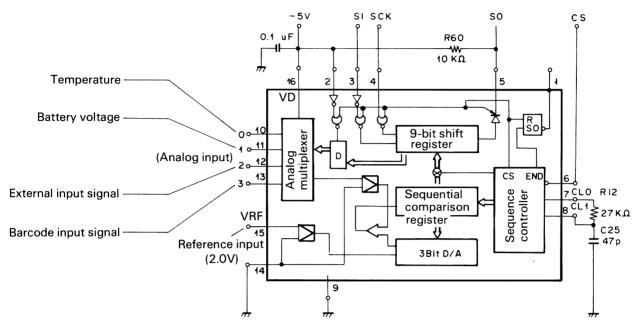

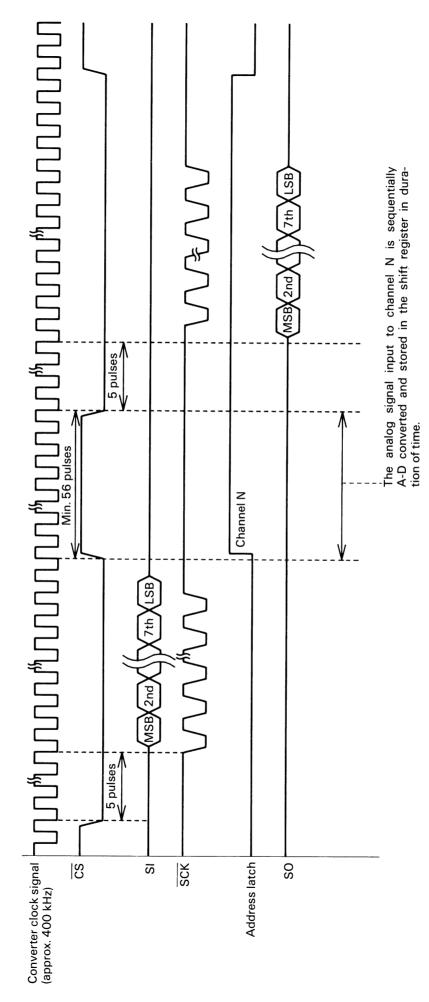

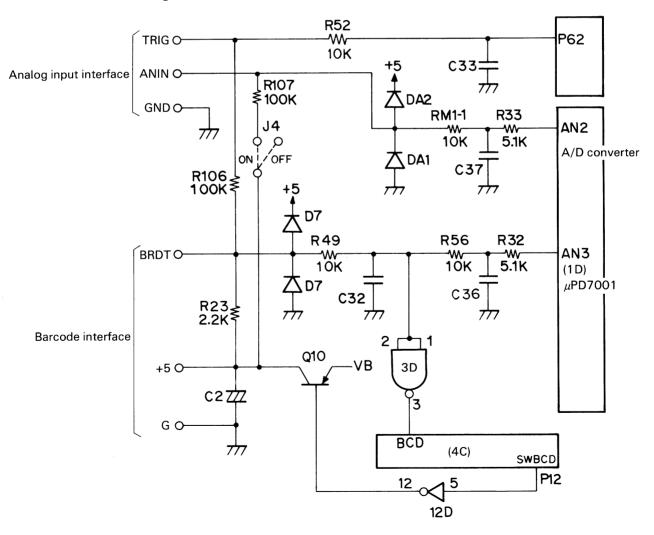

Data such as A-D conversion data which are exchanged between the following components are serially transferred:

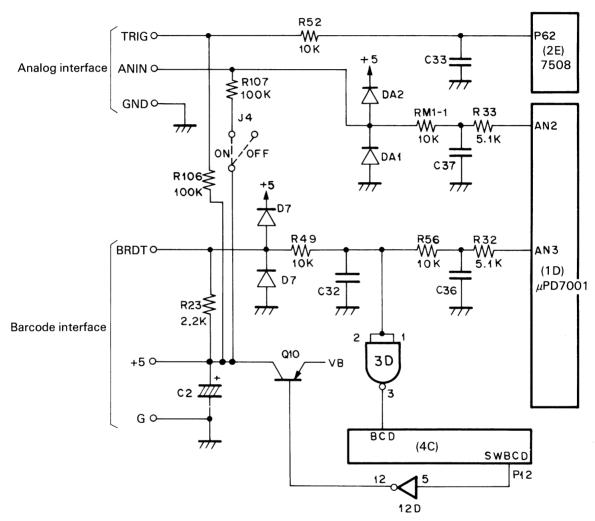

- (1) Between sub-CPU 7508 (2E) and A-D converter 7001 (1D)

- ANO channel selection and temperature data transfer

- AN1 channel selection and battery voltage data transfer

- AN2 channel selection and external analog input data transfer

- AN3 channel selection and barcode data transfer

- (2) Between sub-CPU 7508 (2E) and gate array GAH40M (4C)

- Channel selections listed in (1) above and data transfer

- Keyboard and DIP switch data transfer

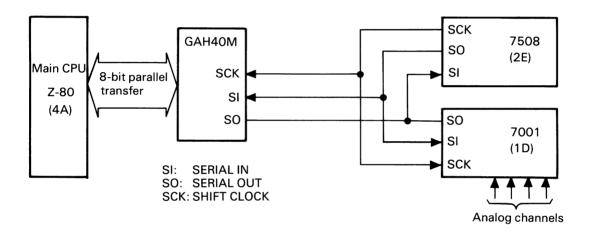

Fig. 2-29 shows the transfer paths of the above serial data.

Fig. 2-29 Serial Data Transfer

The operations listed in (1) and (2) above are controlled by the appropriate commands of the main CPU and the sub-CPU 7508. The operation sequence executed when the main CPU reads data from the A-D converter 7001 is shown below.

- (1) Main CPU reads I/O address 05 and examines whether bit is on (high) examines whether a analog data read command may be issued by checking the state of the handshaking FF in the gate array GAH40M (bit 0 of I/O address 05). If the previous command has been processed, bit 0 is on, indicating that the command may be issued (as signalled by RDY SIO).

- (2) Main CPU writes the 1-byte command at I/O address 06 (SIOR resistor) stores the command in the SIOR register in the gate array GAH40M.

- (3) Main CPU writes bit 1 of I/O address "01" this causes an interrupt to sub-CPU which informs it that the command has been stored in the SIOR register (RDY SIO is reset).

- (4) Sub-CPU issues eight shift clock (SCK) pulses to gate array and reads in the 8-bit command from the SIOR register.

- (5) According to the received command, sub-CPU activates (lowers) the CS signal to the A-D converter to select it and then issues the channel selection data in synchronization with the shift clock.

- (6) Sub-CPU deactivates (raises) the  $\overline{\text{CS}}$  signal to allow the A-D converter to perform the specified A-D conversion. Then, the sub-CPU lowers the  $\overline{\text{CS}}$  signal again and reads in the converted data by issuing eight read shift clock pulses.

- (7) Sub-CPU sends the A-D converted data, in synchronization with the shift clock pulses, to the SIOR register in the gate array GAH40M.

- (8) Main CPU reads I/O address 06 to read in the 1-byte data.

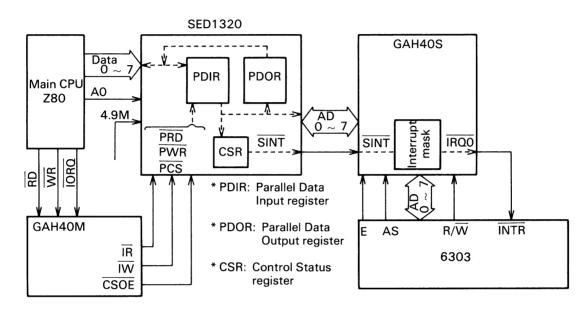

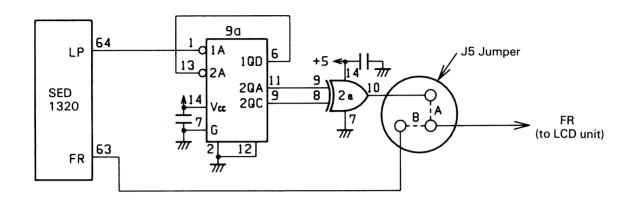

# 2.3.1.2 Data/Command Exchange between Main CPU and Sub-CPU 6303 via SED1320

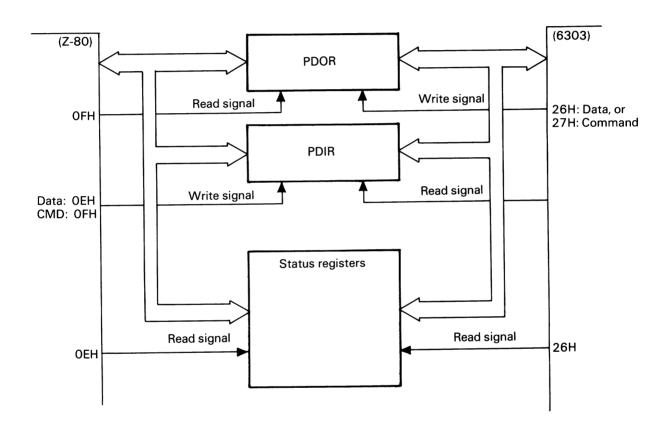

Data/Commands are transferred in an 8-bit parallel format between Z80, the main CPU, and the sub-CPU 6303 via two registers in the gate array SED1320. Fig. 2-30 illustrates the control flow.

Fig. 2-30 Control Flow for Data/Command Transfer between Z80 and 6303

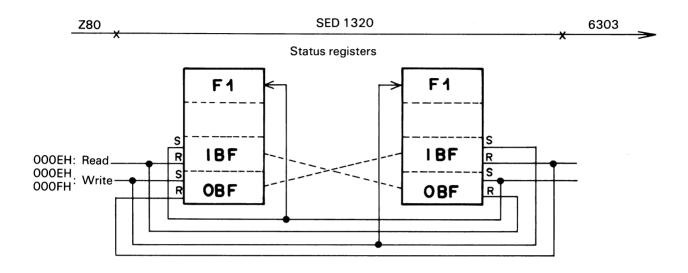

Handshaking between the Z80 and 6303 is performed via the two status registers in SED1320 which are respectively assigned to the CPUs. Each of the registers has Input Buffer Full (IBF), Output Buffer Full (IBF), and Flag (FI) bits as shown in Fig. 2-31. Data outputs (write) and inputs (read) are controlled by the state of these status bits. The handshaking between the two CPUs is explained below.

Fig. 2-31 Handshaking Between Z80 and 6303

The status registers are accessed from both Z80 and are 6303 and used as follows:

# **Output**

When either the Z80 or 6303 outputs 1-byte data, the OBF bit of one status register and the IBF bit of the other status register are set. This informs the other CPU that the 1-byte data has been stored in the gate array SED1320, ready to be read.

#### Input

When the CPU reads the data from SED1320, the IBF bit of its status register and the OBF bit of the other register are reset after the data is read in. These input and output operations are asynchronous.

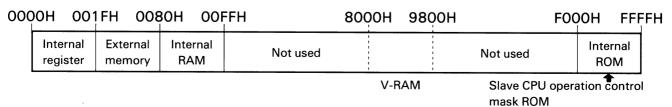

# 2.3.1.3 Memory Space

There is a memory space on the MAPLE board which includes the following RAMs and ROMs:

Fig. 2-32 Memory Space

# 2.3.2 Operations of Main CPU (70008)

The Main CPU Z80 operates using control programs contained in the 32kB ROM (2A) to control the slave CPU 6303, sub-CPU 7508, gate arrays, D-RAM, and serial controller 82C51, etc. The slave and sub-CPUs are controlled via the handshaking gate arrays.

These control operations are accomplished using the I/O addresses listed in table 2-4.

Table 2-4 I/O Address

| I/O adress   | Read/Write<br>access | Circuit component | Function                                   |  |  |  |

|--------------|----------------------|-------------------|--------------------------------------------|--|--|--|

| 0000         | R                    | GAH40M            | Input Capture register (L) command trigger |  |  |  |

| 0000         | W                    | GAH40M            | Control register                           |  |  |  |

| 0001         | R                    | GAH40M            | Input Capture register (H) command trigger |  |  |  |

| 0001         | W                    | GAH40M            | Command register                           |  |  |  |

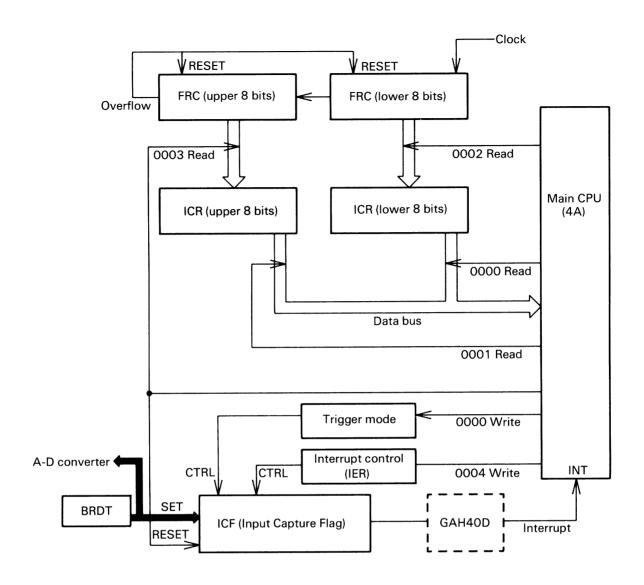

| 0002         | R                    | GAH40M            | Input Capture register (L) barcode trigger |  |  |  |

| 0002         | W                    | GAH40M            | Control register                           |  |  |  |

| 0003         | R                    | GAH40M            | Input Capture register (H) barcode trigger |  |  |  |

| 0004         | R                    | GAH40M            | Interrupt Status register                  |  |  |  |

| 0004         | W                    | GAH40M            | Interrupt Enable register                  |  |  |  |

| 0005         | R                    | GAH40M            | Status register                            |  |  |  |

| 0006         | R                    | GAH40M            | Serial I/O register                        |  |  |  |

| 0000         | W                    |                   | Serial I/O register                        |  |  |  |

| 0007<br>0008 |                      |                   | Unused                                     |  |  |  |

| 000C         | W                    | 82C51             | Command                                    |  |  |  |

| 000D         | R/W                  | 82C51             | Data                                       |  |  |  |

| 000E         | R                    | SED 1320          | Status                                     |  |  |  |

| 000F         | R                    | SED 1320          | Data                                       |  |  |  |

| UUUF         | W                    |                   | Command register                           |  |  |  |

| 0010<br>00FF |                      |                   | Unused                                     |  |  |  |

# 2.3.2.1 Reset

Three negative going swings of the clock signal supplied at the  $\overline{RS}$  terminal cause the internal initialization of the line CPU 70008, which then waits for the reset condition to be removed. When the reset signal is discontinued, the CPU begins executing its program from address 0000H (the start address of the ROM located at 2A). The internal initialization sequence occurs as follows:

- Resetting the Program Counter (PC) to 0000H

- Resetting the Interrupt Enable flipflop (IFF) to 0

- Resetting the Index register (I) and the memory Refresh register (R) to 00

- Resetting the interrupt mode to 0

- Forcing all address/data bus lines in the high impedance state

- Diactivating all control signals

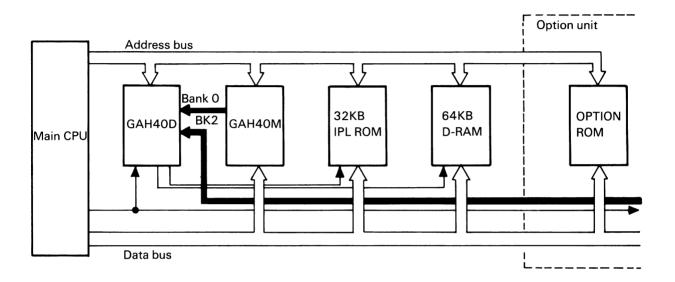

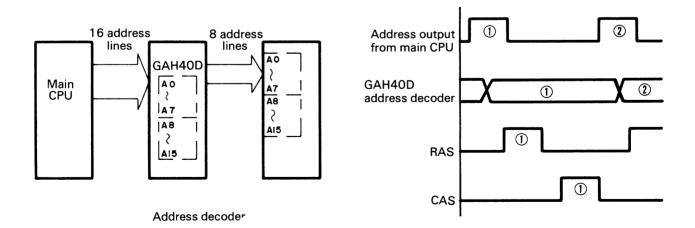

# 2.3.2.2 Memory Bank Switching

The main CPU controls memory using 16 address lines, making it capable accessing a memory space of 64k bytes from address 0000 to FFFF. However, the CPU memory space includes a 32k byte ROM and an option unit ROM, in addition to the 64k byte dynamic RAM. To allow the CPU to access this entire memory space which is greater than 64k bytes, bank switching signals are used.

**Note:** When a RAM disk is used as option unit, no memory back switching is made but the main CPU controls the external RAM as an I/O port.

Fig. 2-33 Memory Configuration

The entire memory space is divided into the four banks (listed in Table 2.5), which are selected by a combination of the BANK 0 and BK 2 signals shown in Fig. 2-32.

BK<sub>2</sub> 1 0 1 0 BANKO 0 1 0 1 Address **FFFF** D-RAM D-RAM **OPTION OPTION** (H) (H) ROM (H) ROM (H) 8000 7FFF **IPL ROM** D-RAM **IPL ROM OPTION** (L) ROM (L) 0000

**Table 2-5 Memory Bank Selection**

As shown in Fig. 2-33, two band control signals, BANK 0 and  $\overline{BK}$  2, are used, both are fed to the gate array GAH40D. Because  $\overline{BK}$  2 is pulled up on the MAPLE board, only the left two D-RAMs and IPL ROM are addressed when no option unit (with ROM) is available.

# **2.3.2.3 Interrupt**

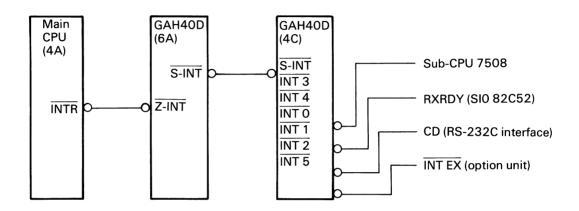

There are only two external interrupt signals to the main CPU; INTR and BURQ. The NMI signal is not used. The main CPU interrupts are discussed in the following.

# 1. INTR interrupts

The INTR interrupts include the interrupts INTO through INT5 from the sub-CPU 7508, the serial controller 82C51, the RS-232C interface, the gate array GAH40M, and the option unit. These interrupts multiplexed by GAH40M and fed to the main CPU as single interrupt request via the gate array GAH40D (Fig. 2-34).

Fig. 2-34 INTR Interrupt Request Routing

The two interrupt requests of INT3 (Input Capture flag) and INT4 (Overflow flag) are generated within GAH40M. All six interrupts are controlled in GAH40M from the main CPU by the corresponding interrupt control bits at I/O address 0004 listed in Table 2-6

| Interrupt<br>control bit | Bit name            | Bit name Interrupt In vector co |   | Bit name             | Interrupt<br>vector |

|--------------------------|---------------------|---------------------------------|---|----------------------|---------------------|

| 7                        | Unused              |                                 | 3 | IER 3 (ICF)          | F6                  |

| 6                        | Unused              | _                               | 2 | IER 2 (RS-232C)      | F4                  |

| 5                        | IER 5 (Option unit) | FA                              | 1 | IER 1 (SIO 82C51)    | F2                  |

| 4                        | IER 4 (OVF)         | F8                              | 0 | IER 0 (sub-CPU 7508) | F0                  |

**Table 2-6 Interrupt Control Bits**

When the INTR signal is generated with the interrupt enabled (i.e., the corresponding IER bit ON), the main CPU enters the interrupt processing program after the current instruction has been executed.

# 2. BURQ interrupt

This interrupt request singal is fed from the option unit o the main CPU. When it goes low, the main CPU forces the address bus, daga bus, and system control terminals (MREQ, IORQ, RD, and WD) in to a high impedance state, making the buses available for use by the option unit after the current instruction has been executed.

<sup>\*</sup>The interrupt request signals and their function summaries are listed in Table 2-7 in priority order.

Table 2-7 Interrupt Request Signal and Their Priority

| Interrupt<br>Priority order | Signal name  | Function                                               | Vector<br>address |

|-----------------------------|--------------|--------------------------------------------------------|-------------------|

| Highest                     | BURQ         | External bus request from option unit                  |                   |

| 1                           | NMI          | Unused                                                 |                   |

|                             | INTR (INT 0) | Alarm and low voltage detection from sub-CPU 7508      | FO                |

|                             | INTR (INT 1) | 1-byte received from serial controller 82C51           | F2                |

|                             | INTR (INT 2) | CD signal from RS-232C interface                       | F4                |

|                             | INTR (INT 3) | Barcode trigger within gate array GAH40M               | F6                |

|                             | INTR (INT 4) | Free running counter overflow within gate array GAH40M | F8                |

| Lowest                      | INTR (INT 5) | Interrupt from option unit                             | FA                |

# 3. Intrerrupt vectors

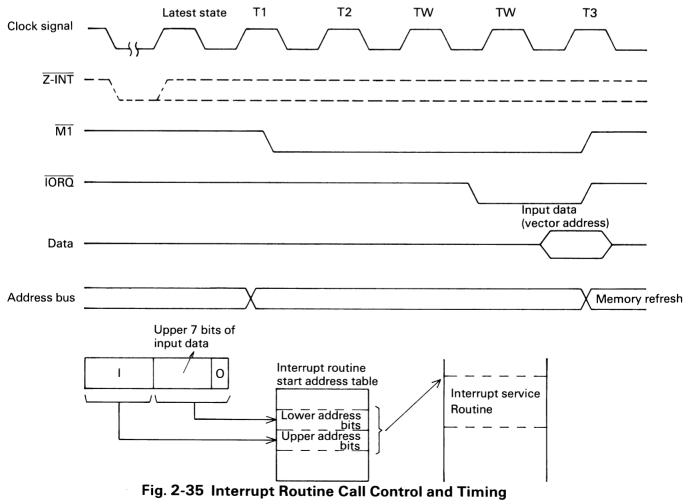

When accepting an enabled interrupt request via the  $\overline{Z\text{-INT}}$  terminal of GAH40D, the main CPU makes an indirect call to the interrupt processing routine using the contents of the I register and the read vector address – this call is called madkable interrupt mode 2 operation.

Fig. 2-35 shows the signal timing from the time the interrupt is accepted until the interrupt routine is entered by the indirect call. A concept of the controlling scheme is also presented.

#### REV.-A

When the Z-INT signal is activated, the main CPU samples the signal at the rising edge of the clock signal in the last state of the current instruction execution and generates an M1 cycle which includes two extra wait cycles. Then, the CPU reads data (a vector address) from GAH40M at the rising edge of T3 in the M1 cycle and begins the interrupt processing.

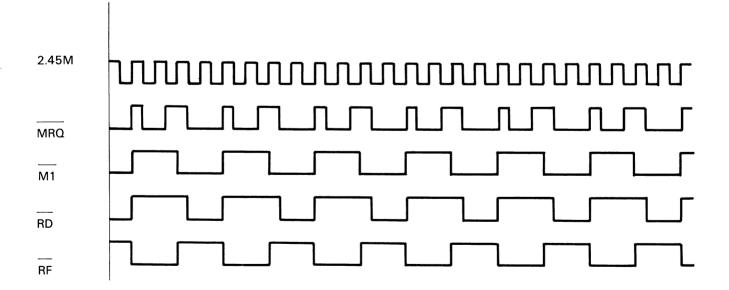

# **Observed Memory Control Signal Waveforms**

(Top) CLK:

Measured at 4A, pin 6

(Second from top) M1:

Measured at 4A, pin 27

(Second from bottom) MRQ

Measured at 4A, pin 19

(Bottom) RF:

Measured at 4A, pin 28

Fig. 2-36 CLK, M1, MRQ, and RF

(Top) CLK:

Measured at 4A, pin 6

(Second from top) MRQ:

Measured at 4A, pin 19

(Second from bottom) RF:

Measured at 4A, pin 28

(Bottom) RD:

Measured at 4A, pin 21

Fig. 2-37 CLK, MRQ, RF, and RD

# **Observed D-RAM Control Signal Waveforms**

(Top) W1:

Measured at 6A, pin 18

(Second form top) RAS1:

Measured at 6A, pin 17

(Second from bottom) CAS1:

Measured at 6A, pin 44

(Bottom) RF:

Measured at 6A, pin 40

# Enlarged

Fig. 2-38 W1, RAS1, CAS1, and RF

# REV.-A

# **Observed D-RAM Refresh Signal Waveforms**

(Top) Z-RF:

Measured at 6A, pin 29

(Bottom) FR:

Measured at 6A, pin 40

# **Enlarged**

Fig. 2-39  $\overline{\text{Z-RF}}$  and  $\overline{\text{RF}}$

# 2.3.3 Operations of Slave CPU 6303

The slave CPU 6303 is an 8-bit CMOS CPU, which controls the microcassette tape (MCT), liquid crystal display (LCD), ROM files, external speaker, and serial interface.

# 2.3.3.1 Operation Modes

The operation mode of the 6303 slave CPU is determined by the state of three ports, P20, P21, and P22. Performance of mode setting is a hardware based function, occurring immediately after power up or whenever the reset switch is pressed. When the reset signal goes high, the CPU latches the state of the three ports in an internal register. When the reset signal is deactivated, the operation mode is determined according to the information latched.

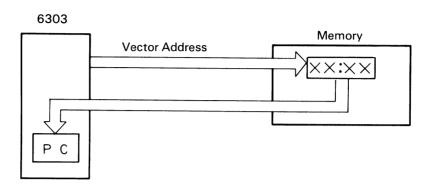

The slave CPU performs the following sequence of operations after each deactivation of the reset signal:

- Latches bits 2, 1, and 0 of port 2 in the Program Control Register.

- Sets the vector address FFFE and the contents of the byte location addressed by FFFF to the program counter.

- Sets the interrupt mask bits.

- A data address is read from the vector address, FFFF, is sent to the program counter, and initiates program execution from that address.

- \* Program Control Register (0003H) stores the state of ports 20, 21, and 22, used for determining the operation mode.

Fig. 2-40 illustrates a sample CPU operation mode selection, mode 6 (multiplexed/partial decode), from the shown combination of port states.

7 6 5 4 1 0 Port 2 data register PC2 PC<sub>1</sub> PC<sub>0</sub> 1/04 1/01 1/00 address 0003H Mode setting port states 13E, pin 56 ······ Low CN3, pin 8 ..... High

Slave CPU 6303 (13D)

Fig. 2-40 Slave CPU Operation Mode Selection Example

+5 .....

High

Mode selection reults in the following memory mapping:

Fig. 2-41 Resultant Memory Mapping Example

# REV.-A

# Fig. 2-42 illustrates the vector address operation.

<sup>\*</sup> Vector address – program counter

<sup>\*</sup> The CPU stores the contents of the location addressed by the vector address in the program counter.

Fig. 2-42 Vector Address Operation

# 2.3.3.2 Internal Registers and External Memories

Tabel 2-8 lists the internal registers and external memory locations whitch are used as various control addresses.

**Table 2-8 Internal Registers and External Momory Locations**

|   | Address | Function                               | Read/ |                              | *****                        |                | Е             | Bit           |         |              |             |

|---|---------|----------------------------------------|-------|------------------------------|------------------------------|----------------|---------------|---------------|---------|--------------|-------------|

|   | Address | Function                               | Write | 7                            | 6                            | 5              | 4             | 3             | 2       | 1            | 0           |

|   | 0000    | I/O port 1 data direction register     |       |                              | I/O Control For Address 0002 |                |               |               |         |              |             |

|   | 0001    | I/O port 2 data direction register     |       | I/O control for address 0003 |                              |                |               |               |         |              |             |

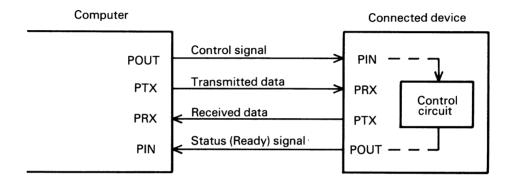

| 6 | 0002    | I/O port 1 port address                |       | Speaker<br>power<br>supply   | Speaker<br>output            | SERIAL<br>POUT | SERIAL<br>PIN | μMCT<br>HSW   | μMCT WE | μMCT<br>ERAH | μMCT<br>HMT |

| 3 | 0003    | I/O port 2 port address                |       | _                            |                              | _              | SERIAL<br>PTX | SERIAL<br>PRX | _       | μMCT WD      | PRD         |

|   | 0004    | I/O port 3 data direction register     |       | I/O control for address 0006 |                              |                |               |               |         |              |             |

| 0 | 0005    | I/O port 4 data direction register     |       |                              |                              | I/O co         | ontrol for    | address       | 0007    |              |             |

|   | 0006    | I/O port 3 port address                |       |                              |                              | Addres         | s (lower      | 8 bits)/d     | ata bus |              |             |

| 3 | 0007    | I/O port 4 port address                |       |                              |                              | Add            | ress bus      | (upper 8      | bits)   |              |             |

|   | 0008    | Timer control/status register          |       |                              |                              |                |               |               |         |              |             |

|   | 0009    | Counter (upper 8 bits)                 |       | Bit 15                       | Bit 14                       | Bit 13         | Bit 12        | Bit 11        | Bit 10  | Bit 9        | Bit 8       |

|   | 000A    | Counter (lower 8 bits)                 |       | Bit 7                        | Bit 6                        | Bit 5          | Bit 4         | Bit 3         | Bit 2   | Bit 1        | Bit O       |

|   | 000B    | Output compare register (upper 8 bits) |       | Bit 15                       | Bit 14                       | Bit 13         | Bit 12        | Bit 11        | Bit 10  | Bit 9        | Bit 8       |

|   | 000C    | Output compare register (lower 8 bits) |       | Bit 7                        | Bit 6                        | Bit 5          | Bit 4         | Bit 3         | Bit 2   | Bit 1        | Bit O       |

|        | Address | Function                                 | Read/ |                   |               |                  | Е                   | Bit                 |                     |                   |                 |

|--------|---------|------------------------------------------|-------|-------------------|---------------|------------------|---------------------|---------------------|---------------------|-------------------|-----------------|

|        | Address | runction                                 | Write | 7                 | 6             | 5                | 4                   | 3                   | 2                   | 1                 | 0               |

|        | 000D    | Input Capture register (upper 8 bits)    |       | Bit15             | Bit 14        | Bit 13           | Bit 12              | Bit 11              | Bit 10              | Bit 9             | Bit 8           |

|        | 000E    | Input Capture register<br>(lower 8 bits) |       | Bit 7             | Bit 6         | Bit5             | Bit 4               | Bit 3               | Bit 2               | Bit 1             | Bit O           |

| 6      | 000F    | Control/status register                  |       | FLAG              | IRQ<br>enable |                  | oss                 | LATCH enable        | _                   |                   | _               |

| 0      | 0010    | Baudrate/Mode Control register           |       |                   | _             | _                |                     | Clock               | control             | Baudrat           | e control       |

| 3      | 0011    | TX and RX control/status register        |       | RDRF              | ORFE          | TDRE             | RIE                 | RE                  | TIE                 | TE                | WU              |

|        | 0012    | Receive data register                    |       | MSB               |               |                  |                     |                     |                     |                   | LSB             |

|        | 0013    | Transmit data register                   |       | MSB               |               |                  |                     |                     |                     |                   | LSB             |

|        | 0014    | RAM control register                     |       | Stand-by<br>power | RAM<br>enable |                  | _                   | _                   | _                   | _                 | _               |

|        | 0020    | Counter (upper byte)                     | R     | CNTR<br>Count     |               | _                | Micro<br>Bit 12     | cassette<br>Bit 11  | tape driv<br>Bit 10 | e counte<br>Bit 9 | r data<br>Bit 8 |

|        |         | Counter reset                            | W     | _                 | _             | _                |                     | _                   |                     |                   | _               |

| G<br>A |         | Counter (lower byte)                     | R     | Bit 7             | Bit 6         | Microca<br>Bit 5 | assette ta<br>Bit 4 | ape coun            | ter data<br>Bit 2   | Bit 1             | BitO            |

| Н      | 0021    | Command register                         | w     | STOP<br>CNT       | FAST          |                  | МТС                 | МТВ                 | MTA                 | SW<br>MCT         | SW PR           |

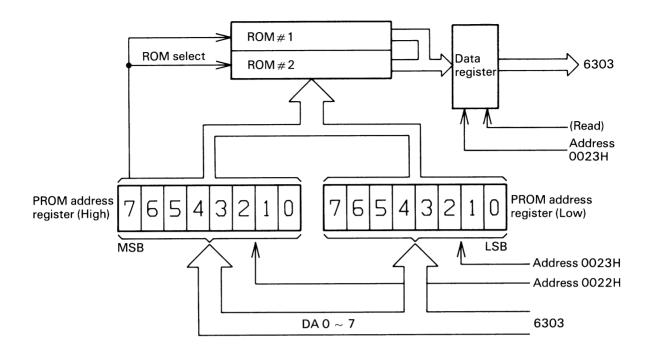

| 0      | 0022    | P-ROM address (upper 8 byte)             | w     | Bit 15            | Bit 14        | Uppe<br>Bit 13   | er P-ROM<br>Bit 12  | 1 address<br>Bit 11 | bits<br>Bit 10      | Bit 9             | Bit 8           |

| s      | 0023    | P-ROM address (lower 8 byte)             | w     | Bit 7             | Bit 6         | Uppo<br>Bit 5    | er P-ROM<br>Bit 4   | 1 address<br>Bit 3  | bits<br>Bit 2       | Bit 1             | Bit O           |

|        |         | P-ROM read data                          | R     | MSB               |               |                  |                     |                     |                     |                   | LSB             |

| S      | 0024    | Controller instruction register          | w     |                   |               |                  |                     |                     |                     |                   |                 |

| E      | 0025    | Controller data buffer                   | R     |                   |               |                  |                     |                     |                     |                   |                 |

| D      |         | Controller data buffer                   | w     |                   |               |                  |                     |                     |                     |                   |                 |

| -      |         | Controller status register               | R     |                   |               |                  |                     |                     |                     |                   |                 |

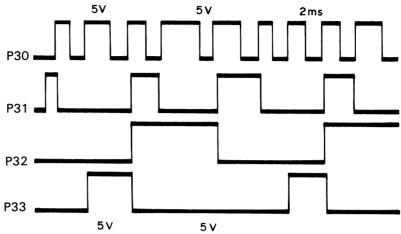

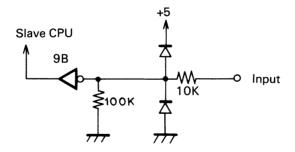

| 3      | 0026    | Port data output register (data)         | w     |                   |               |                  |                     |                     |                     | _                 |                 |