# Q VAX Instruction Set

The following sections describe the native-mode instruction set. The instructions are divided into groups according to their function and are listed alphabetically within each group.

### 9.1 Introduction to the VAX Instruction Set

This section describes the instructions generally used by all software across all implementations of the VAX architecture.

You can find a more complete description of the instruction set in the VAX Architecture Reference Manual. The VAX Architecture Reference Manual also contains information on instructions that are generally used by privileged software and are specific to specialized portions of the VAX architecture, such as memory management, interrupts and exceptions, process dispatching, and processor registers.

A list of instructions and opcode assignments appears in Appendix D.

## 9.2 Instruction Descriptions

The instruction set is divided into the following 12 major sections:

- Integer arithmetic and logical

- Address

- · Variable-length bit field

- Control

- Procedure call

- Miscellaneous

- Queue

- Floating point

- Character string

- Cyclic redundancy check (CRC)

- Decimal string

- Edit

Within each major section, instructions that are closely related are combined into groups and described together. The instruction group description is composed of the following:

• The group name.

### **VAX Instruction Set**

### 9.2 Instruction Descriptions

- The format of each instruction in the group, including the name and type of each instruction operand specifier and the order in which it appears in memory. Operand specifiers from left to right appear in increasing memory addresses.

- The effect on condition codes.

- Exceptions specific to the instruction. Exceptions that are generally possible for all instructions (for example, illegal or reserved addressing mode, T-bit, and memory management violations) are not listed.

- The opcodes, mnemonics, and names of each instruction in the group. The opcodes are given in hexadecimal.

- A description, in English, of the instruction.

- Optional notes on the instruction and programming examples.

#### **Operand Specifier Notation**

Operand specifiers are described as follows:

name . access-type data-type

#### name

A mnemonic name for the operand in the context of the instruction. The name is often abbreviated.

#### access-type

A letter denoting the operand specifier access type:

- a Calculate the effective address of the specified operand. Address is returned in a longword that is the actual instruction operand. Context of address calculation is given by **data-type**; that is, size to be used in autoincrement, autodecrement, and indexing.

- b No operand reference. Operand specifier is a branch displacement. Size of branch displacement is given by **data-type**.

- m Operand is read, potentially modified, and written. Note that this is *not* an indivisible memory operation. Also note that if the operand is not actually modified, it may not be written back. However, modify type operands are always checked for both read and write accessibility.

- r Operand is read only.

- v Calculate the effective address of the specified operand. If the effective address is in memory, the address is returned in a longword that is the actual instruction operand. Context of address calculation is given by **data-type**. If the effective address is Rn, the operand is in Rn or R[n+1]'Rn.

- w Operand is written only.

#### data-type

A letter denoting the data type of the operand:

- b Byte

- d D\_floating

- f F floating

- g G\_floating

# VAX Instruction Set 9.2 Instruction Descriptions

h H\_floating

l Longword

o Octaword

q Quadword

w Word

x First data type specified by instruction

y Second data type specified by instruction

### **Operation Description Notation**

The operation of an instruction is given as a sequence of control and assignment statements in an ALGOL-like syntax. No attempt is made to formally define the syntax; it is assumed to be familiar to the reader. The notation used is an extension of the notation introduced in Section 8.6.

Addition Subtraction, unary minus Multiplication Division (quotient only) Exponentiation Concatenation Is replaced by <-Is defined as Contents of register Rn Rn or R[n] PC, SP, FP, or AP The contents of register R15, R14, R13, or R12, respectively The contents of the processor status word **PSW** The contents of the processor status longword **PSL** Contents of memory location whose address is x (x) Contents of memory location whose address is x; x (x)+incremented by the size of operand referenced at x x decremented by size of operand to be referenced at -(x)x; contents of memory location whose address is x A modifier that delimits an extent from bit position x to <x:y> bit position y inclusive A modifier that enumerates bits x1,x2,...,xn <x1,x2,...,xn> Arithmetic parentheses used to indicate precedence {} Logical AND AND Logical OR OR Logical XOR **XOR** Logical (one's) complement NOT Less than signed LSS Less than unsigned LSSU

### VAX Instruction Set

### 9.2 Instruction Descriptions

LEQ Less than or equal signed LEQU Less than or equal unsigned

EQL Equal signed

EQLU Equal unsigned

NEQ Not equal signed

NEQU Not equal unsigned

GEQU Greater than or equal signed

GEQU Greater than or equal unsigned

GTR Greater than signed GTRU Greater than unsigned

SEXT(x) x is sign extended to size of operand needed

ZEXT(x) x is zero extended to size of operand needed

REM(x,y) Remainder of x divided by y, such that x/y and

REM(x,y) have the same sign

MINU(x,y) Minimum unsigned of x and y MAXU(x,y) Maximum unsigned of x and y

#### Use the following conventions:

- Other than alterations caused by (x)+, or -(x), and the advancement of the program counter (PC), only operands or portions of operands appearing on the left side of assignment statements are affected.

- No operator precedence is assumed, except that replacement (<-) has the lowest precedence. Precedence is indicated explicitly by { }.

- All arithmetic, logical, and relational operators are defined in the context of their operands. For example, "+" applied to floating operands means a floating add, while "+" applied to byte operands is an integer byte add. Similarly, "LSS" is a floating comparison when applied to floating operands, while "LSS" is an integer byte comparison when applied to byte operands.

- Instruction operands are evaluated according to the operand specifier conventions (see Chapter 8). The order in which operands appear in the instruction description has no effect on the order of evaluation.

- Condition codes generally indicate the effect of an operation on the value of actual stored results, not on "true" results (which might be generated internally to greater precision). For example, two positive integers can be added together and the sum stored as a negative value because of overflow. The condition codes indicate a negative value even though the "true" result is clearly positive.

# 9.2.1 Integer Arithmetic and Logical Instructions

The following instructions are described in this section:

|     | Description and Opcode                                                   | Number of<br>Instructions |

|-----|--------------------------------------------------------------------------|---------------------------|

| 1.  | Add Aligned Word<br>ADAWI add.rw, sum.mw                                 | 1                         |

| 2.  | Add 2 Operand<br>ADD{B,W,L}2 add.rx, sum.mx                              | 3                         |

| 3.  | Add 3 Operand<br>ADD{B,W,L}3 add1.rx, add2.rx, sum.wx                    | 3                         |

| 4.  | Add with Carry ADWC add.rl, sum.ml                                       | 1                         |

| 5.  | Arithmetic Shift ASH{L,Q} cnt.rb, src.rx, dst.wx                         | 2                         |

| 6.  | Bit Clear 2 Operand<br>BIC{B,W,L}2 mask.rx, dst.mx                       | 3                         |

| 7.  | Bit Clear 3 Operand<br>BIC{B,W,L}3 mask.rx, src.rx, dst.wx               | 3                         |

| 8.  | Bit Set 2 Operand<br>BIS{B,W,L}2 mask.rx, dst.mx                         | 3                         |

| 9.  | Bit Set 3 Operand<br>BIS{B,W,L}3 mask.rx, src.rx, dst.wx                 | 3                         |

| 10. | Bit Test BIT{B,W,L} mask.rx, src.rx                                      | 3                         |

| 11. | Clear<br>CLR{B,W,L,Q,O} dst.wx                                           | 5                         |

| 12. | Compare CMP{B,W,L} src1.rx, src2.rx                                      | 3                         |

| 13. | Convert<br>CVT{B,W,L}{B,W,L} src.rx, dst.wy<br>All pairs except BB,WW,LL | 6                         |

| 14. | Decrement DEC{B,W,L} dif.mx                                              | 3                         |

| 15. | Divide 2 Operand<br>DIV{B,W,L}2 divr.rx, quo.mx                          | 3                         |

| 16. | Divide 3 Operand<br>DIV{B,W,L}3 divr.rx, divd.rx, quo.wx                 | 3                         |

| 17. | Extended Divide EDIV divr.rl, divd.rq, quo.wl, rem.wl                    | 1                         |

| 18. | Extended Multiply EMUL mulr.rl, muld.rl, add.rl, prod.wq                 | 1                         |

| 19. | Increment<br>INC{B,W,L} sum.mx                                           | 3                         |

| 20. | Move Complemented MCOM{B,W,L} src.rx, dst.wx                             | 3                         |

# **VAX Instruction Set**

# 9.2 Instruction Descriptions

|     | Description and Opcode                                      | Number of<br>Instructions |

|-----|-------------------------------------------------------------|---------------------------|

| 21. | Move Negated<br>MNEG{B,W,L} src.rx, dst.wx                  | 3                         |

| 22. | Move<br>OV{B,W,L,Q} src.rx, dst.wx                          | 4                         |

| 23. | Move Zero-Extended<br>MOVZ{BW,BL,WL} src.rx, dst.wy         | 3                         |

| 24. | Multiply 2 Operand<br>MUL{B,W,L}2 mulr.rx, prod.mx          | 3                         |

| 25. | Multiply 3 Operand<br>MUL{B,W,L}3 mulr.rx, muld.rx, prod.wx | 3                         |

| 26. | Push Long<br>PUSHL src.rl, {-(SP).wl}                       | 1                         |

| 27. | Rotate Long<br>ROTL cnt.rb, src.rl, dst.wl                  | 1                         |

| 28. | Subtract with Carry<br>SBWC sub.rl, dif.ml                  | 1                         |

| 29. | Subtract 2 Operand<br>SUB{B,W,L}2 sub.rx, dif.mx            | 3                         |

| 30. | Subtract 3 Operand<br>SUB{B,W,L}3 sub.rx, min.rx, dif.wx    | 3                         |

| 31. | Test<br>TST{B,W,L} src.rx                                   | 3                         |

| 32. | Exclusive OR 2 Operand XOR{B,W,L}2 mask.rx, dst.mx          | 3                         |

| 33. | Exclusive OR 3 Operand XOR{B,W,L}3 mask.rx, src.rx, dst.wx  | 3                         |

## **ADAWI**

Add Aligned Word Interlocked

| FORMAT          | opcode add.rw, sum.mw                                                                        |   |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------|---|--|--|--|

| condition codes | N ← sum LSS 0; Z ← sum EQL 0; V ← {integer overflow}; C ← {carry from most-significant bit}; | - |  |  |  |

| exceptions      | reserved operand fault integer overflow                                                      |   |  |  |  |

| opcodes         | 58 ADAWI Add Aligned Word Interlocked                                                        | _ |  |  |  |

## **DESCRIPTION**

The addend operand is added to the sum operand, and the sum operand is replaced by the result. The operation is interlocked against similar operations on other processors in a multiprocessor system. The destination must be aligned on a word boundary; that is, bit 0 of the address of the sum operand must be zero. If it is not, a reserved operand fault is taken.

- 1 Integer overflow occurs if the input operands to the add have the same sign, and the result has the opposite sign. On overflow, the sum operand is replaced by the low-order bits of the true result.

- 2 If the addend and the sum operands overlap, the result and the condition codes are UNPREDICTABLE.

# **VAX Instruction Set ADD**

## **ADD**

Add

| FORMAT          | •                          | erand:<br>erand:                                   | opcode<br>opcode | add.rx, sum.mx<br>add1.rx, add2.rx, sum.wx                                                                        |  |  |

|-----------------|----------------------------|----------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| condition codes | Z 4                        | sum LSS<br>sum EQ<br>{integer<br>{carry fro        | L 0;             | int bit};                                                                                                         |  |  |

| exceptions      | integer overflow           |                                                    |                  |                                                                                                                   |  |  |

| opcodes         | 80<br>81<br>A0<br>A1<br>C0 | ADDB2<br>ADDB3<br>ADDW2<br>ADDW3<br>ADDL2<br>ADDL3 |                  | Add Byte 2 Operand Add Byte 3 Operand Add Word 2 Operand Add Word 3 Operand Add Long 2 Operand Add Long 3 Operand |  |  |

## **DESCRIPTION**

In 2 operand format, the addend operand is added to the sum operand and the sum operand is replaced by the result. In 3 operand format, the addend 1 operand is added to the addend 2 operand and the sum operand is replaced by the result.

#### Note

Integer overflow occurs if the input operands to the add have the same sign and the result has the opposite sign. On overflow, the sum operand is replaced by the low-order bits of the true result.

## **ADWC**

Add with Carry

| FORMAT          | opcode add.rl, sum.ml                                                                        |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------|--|--|--|--|

| condition codes | N ← sum LSS 0; Z ← sum EQL 0; V ← {integer overflow}; C ← {carry from most-significant bit}; |  |  |  |  |

| exceptions      | integer overflow                                                                             |  |  |  |  |

| opcodes         | D8 ADWC Add with Carry                                                                       |  |  |  |  |

### **DESCRIPTION**

The contents of the condition code C-bit and the addend operand are added to the sum operand and the sum operand is replaced by the result.

- 1 On overflow, the sum operand is replaced by the low-order bits of the true result.

- 2 The two additions in the operation are performed simultaneously.

## **ASH**

Arithmetic Shift

| FORMAT          | opcode cnt.rb, src.rx, dst.wx |                                                         |                                             |  |  |

|-----------------|-------------------------------|---------------------------------------------------------|---------------------------------------------|--|--|

| condition codes |                               | ← dst LSS 0;<br>← dst EQL 0;<br>← {integer over<br>← 0; | rflow};                                     |  |  |

| exceptions      | i                             | nteger overflow                                         | 7                                           |  |  |

| opcodes         | 78<br>79                      | ASHL<br>ASHQ                                            | Arithmetic Shift Long Arithmetic Shift Quad |  |  |

### **DESCRIPTION**

The source operand is arithmetically shifted by the number of bits specified by the count operand and the destination operand is replaced by the result. The source operand is unaffected. A positive count operand shifts to the left, bringing zeros into the least significant bit. A negative count operand shifts to the right, bringing in copies of the most significant (sign) bit into the most significant bit. A zero count operand replaces the destination operand with the unshifted source operand.

- 1 Integer overflow occurs on a left shift if any bit shifted into the sign bit position differs from the sign bit of the source operand.

- 2 If cnt GTR 32 (ASHL) or cnt GTR 64 (ASHQ), the destination operand is replaced by zero.

- 3 If cnt LEQ -31 (ASHL) or cnt LEQ -63 (ASHQ), all the bits of the destination operand are copies of the sign bit of the source operand.

| _            | - | _  |

|--------------|---|----|

| О            | 1 |    |

| $\mathbf{r}$ | 1 | ι. |

Bit Clear

| FORMAT          | •      | erand:<br>erand:                       | opcode<br>opcode | mask.rx, dst.mx<br>mask.rx, src.rx, dst.wx |

|-----------------|--------|----------------------------------------|------------------|--------------------------------------------|

| condition codes | Z<br>V | ← dst LSS<br>← dst EQL<br>← 0;<br>← C; |                  |                                            |

| exceptions      | N      | lone.                                  |                  |                                            |

| opcodes         | 8A     | BICB2                                  |                  | Bit Clear Byte                             |

|                 | 8B     | BICB3                                  |                  | Bit Clear Byte                             |

|                 | AA     | BICW2                                  |                  | Bit Clear Word                             |

|                 | AB     | BICW3                                  |                  | Bit Clear Word                             |

|                 | CA     | BICL2                                  |                  | Bit Clear Long                             |

|                 | СВ     | BICL3                                  |                  | Bit Clear Long                             |

## **DESCRIPTION**

In 2 operand format, the result of the logical AND on the destination operand and the one's complement of the mask operand replaces the destination operand. In 3 operand format, the result of the logical AND on the source operand and the one's complement of the mask operand replaces the destination operand.

# **VAX Instruction Set BIS**

# **BIS**

Bit Set

| FORMAT          | 2operano<br>3operano                                | • | mask.rx, dst.mx<br>mask.rx, src.rx, dst.wx                                                                                                |

|-----------------|-----------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------|

| condition codes | N ← dst I Z ← dst I V ← 0; C ← C;                   |   |                                                                                                                                           |

| exceptions      | None.                                               |   |                                                                                                                                           |

| opcodes         | 88 BISB2 89 BISB3 A8 BISW A9 BISW C8 BISL2 C9 BISL3 | 2 | Bit Set Byte 2 Operand Bit Set Byte 3 Operand Bit Set Word 2 Operand Bit Set Word 3 Operand Bit Set Long 2 Operand Bit Set Long 3 Operand |

## **DESCRIPTION**

In 2 operand format, the result of the logical OR on the mask operand and the destination operand replaces the destination operand. In 3 operand format, the result of the logical OR on the mask operand and the source operand replaces the destination operand.

# **BIT**

Bit Test

| FORMAT          | opcode mask.rx, src.rx |                                              |                                                 |  |

|-----------------|------------------------|----------------------------------------------|-------------------------------------------------|--|

| condition codes | Z<br>V                 | ← tmp LSS 0;<br>← tmp EQL 0;<br>← 0;<br>← C; |                                                 |  |

| exceptions      | N                      | None.                                        |                                                 |  |

| opcodes         | 93<br>B3<br>D3         | BITB<br>BITW<br>BITL                         | Bit Test Byte<br>Bit Test Word<br>Bit Test Long |  |

### **DESCRIPTION**

The logical AND is performed on the mask operand and the source operand. Both operands are unaffected. The only action is to modify condition codes.

# **VAX Instruction Set** CLR

# **CLR**

Clear

| FORMAT          | opco                         | ode                                  | dst.wx |                                                                    | ı |  |

|-----------------|------------------------------|--------------------------------------|--------|--------------------------------------------------------------------|---|--|

| condition codes | Z ←<br>V ←                   | — 0;<br>— 1;<br>— 0;<br>— C;         |        |                                                                    |   |  |

| exceptions      | No                           | one.                                 |        |                                                                    |   |  |

| opcodes         | 94<br>B4<br>D4<br>7C<br>7CFD | CLRB<br>CLRW<br>CLRL<br>CLRQ<br>CLRO | •      | Clear Byte<br>Clear Word<br>Clear Long<br>Clear Quad<br>Clear Octa |   |  |

## **DESCRIPTION**

The destination operand is replaced by zero.

### Note

CLRx dst is equivalent to MOVx S^#0, dst, but is 1 byte shorter.

# **CMP**

Compare

| FORMAT          | opo            | ode src1                                                    | .rx, src2.rx                                 |

|-----------------|----------------|-------------------------------------------------------------|----------------------------------------------|

| condition codes | Z<br>V         | ← src1 LSS src2<br>← src1 EQL src<br>← 0;<br>← src1 LSSU sr | 2;                                           |

| exceptions      |                | None.                                                       |                                              |

| opcodes         | 91<br>B1<br>D1 | CMPB<br>CMPW<br>CMPL                                        | Compare Byte<br>Compare Word<br>Compare Long |

## **DESCRIPTION**

The source 1 operand is compared with the source 2 operand. The only action is to modify the condition codes.

## **CVT**

Convert

| FORMAT          | opo              | ode :                                        | src.rx, dst.wy |                    |

|-----------------|------------------|----------------------------------------------|----------------|--------------------|

| condition codes | N<br>Z<br>V<br>C | ← dst LSS<br>← dst EQI<br>← {integer<br>← 0; | L 0;           |                    |

| exceptions      | i                | nteger over                                  | rflow          |                    |

| opcodes         | 99               | CVTBW                                        | Cor            | nvert Byte to Word |

|                 | 98               | CVTBL                                        |                | nvert Byte to Long |

|                 | 33               | CVTWB                                        | Cor            | nvert Word to Byte |

|                 | 32               | CVTWL                                        | Cor            | nvert Word to Long |

|                 | F6               | CVTLB                                        | Cor            | nvert Long to Byte |

|                 | F7               | CVTLW                                        | Cor            | overt Long to Word |

### **DESCRIPTION**

The source operand is converted to the data type of the destination operand and the destination operand is replaced by the result. Conversion of a shorter data type to a longer one is done by sign extension; conversion of longer data type to a shorter one is done by truncation of the higher-numbered (most significant) bits.

#### Note

Integer overflow occurs if any truncated bits of the source operand are not equal to the sign bit of the destination operand.

# **DEC**

Decrement

| FORMAT          | opc            | ode dif.mx                                                                   |                                              |  |  |  |

|-----------------|----------------|------------------------------------------------------------------------------|----------------------------------------------|--|--|--|

| condition codes | V              | ← dif LSS 0;<br>← dif EQL 0;<br>← {integer overflow};<br>← {borrow into most |                                              |  |  |  |

| exceptions      | i              | integer overflow                                                             |                                              |  |  |  |

| opcodes         | 97<br>B7<br>D7 | DECB<br>DECW<br>DECL                                                         | Decrement Byte Decrement Word Decrement Long |  |  |  |

### **DESCRIPTION**

One is subtracted from the difference operand, and the difference operand is replaced by the result.

- 1 Integer overflow occurs if the largest negative integer is decremented. On overflow, the difference operand is replaced by the largest positive integer.

- 2 DECx dif is equivalent to SUBx S $^{1}$ , dif, but is 1 byte shorter.

## DIV

Divide

| FORMAT                | •               | erand:<br>erand:                             | opcode<br>opcode          | divr.rx, quo.mx<br>divr.rx, divd.rx, quo.w  |

|-----------------------|-----------------|----------------------------------------------|---------------------------|---------------------------------------------|

| ondition codes        |                 | 0.0                                          |                           |                                             |

|                       |                 | ← quo LSS                                    |                           |                                             |

|                       | <del></del>     | quo EQl<br>(integer                          | c u,<br>overflow} OR {div | r EOL Ob                                    |

|                       |                 |                                              | overnow) On (un           | VI EQL 0},                                  |

|                       | C 4             | <b></b> 0;                                   |                           |                                             |

|                       | C •             | — U,<br>———————————————————————————————————  |                           |                                             |

| exceptions            | in              | teger over                                   |                           | · · · · · · · · · · · · · · · · · · ·       |

| exceptions            | in              | teger over                                   |                           |                                             |

| •                     | in<br>di        | teger over                                   | ro                        | Divide Pute 2 Operand                       |

| ·                     | in<br>di<br>——— | teger over<br>vide by zer                    | ro                        | Divide Byte 2 Operand                       |

| ·                     | in di           | oteger over<br>vide by zer<br>DIVB2<br>DIVB3 | ro                        | Divide Byte 3 Operand                       |

| ·                     | in di           | DIVB2 DIVW2                                  | ro                        | Divide Byte 3 Operand Divide Word 2 Operand |

| exceptions<br>opcodes | in di           | oteger over<br>vide by zer<br>DIVB2<br>DIVB3 | ro                        | Divide Byte 3 Operand                       |

## **DESCRIPTION**

In 2 operand format, the quotient operand is divided by the divisor operand, and the quotient operand is replaced by the result. In 3 operand format, the dividend operand is divided by the divisor operand, and the quotient operand is replaced by the result.

- 1 Division is performed so that the remainder has the same sign as the dividend; that is, the result is truncated toward zero. (Note that a remainder of zero is not saved.)

- 2 Integer overflow occurs only if the largest negative integer is divided by −1. On overflow, operands are affected as in note 3 following.

- 3 If the divisor operand is zero, then in 2 operand format the quotient operand is not affected; in 3 operand format the quotient operand is replaced by the dividend operand.

## **EDIV**

**Extended Divide**

| FORMAT          | opcode divr.rl, divd.rq, quo.wl, rem.wl                                      |

|-----------------|------------------------------------------------------------------------------|

| condition codes | N ← quo LSS 0; Z ← quo EQL 0; V ← {integer overflow} OR {divr EQL 0}; C ← 0; |

| exceptions      | integer overflow<br>divide by zero                                           |

| opcodes         | 7B EDIV Extended Divide                                                      |

### **DESCRIPTION**

The dividend operand is divided by the divisor operand, the quotient operand is replaced by the quotient, and the remainder operand is replaced by the remainder.

- 1 The division is performed such that the remainder operand (unless it is zero) has the same sign as the dividend operand.

- 2 On overflow, the operands are affected as in note 3, following.

- 3 If the divisor operand is zero, then the quotient operand is replaced by bits 31:0 of the dividend operand, and the remainder operand is replaced by zero.

# **VAX Instruction Set EMUL**

# **EMUL**

**Extended Multiply**

| FORMAT          | орсо       | de m                                     | ulr.rl, muld.rl, add.rl, prod.wq |

|-----------------|------------|------------------------------------------|----------------------------------|

| condition codes | Z ←<br>V ← | — prod LSS<br>— prod EQL<br>— 0;<br>— 0; |                                  |

| exceptions      | No         | ne.                                      |                                  |

| opcodes         | 7A         | EMUL                                     | Extended Multiply                |

| DECODIDEION     | m)         | 14: 1: 1                                 |                                  |

### **DESCRIPTION**

The multiplicand operand is multiplied by the multiplier operand, giving a double-length result. The addend operand is sign extended to double length and added to the result. The product operand is replaced by the final result.

## **INC**

Increment

| FORMAT          | opc            | ode sum.                                                               | mx                                           |

|-----------------|----------------|------------------------------------------------------------------------|----------------------------------------------|

| condition codes | Z<br>V         | ← sum LSS 0;<br>← sum EQL 0;<br>← {integer overflo<br>← {carry from mo | •                                            |

| exceptions      | i              | nteger overflow                                                        |                                              |

| opcodes         | 96<br>B6<br>D6 | INCB<br>INCW<br>INCL                                                   | Increment Byte Increment Word Increment Long |

### **DESCRIPTION**

One is added to the sum operand and the sum operand is replaced by the result.

- 1 Arithmetic overflow occurs if the largest positive integer is incremented. On overflow, the sum operand is replaced by the largest negative integer.

- 2 INCx sum is equivalent to ADDx  $S^{1}$ , sum, but is 1 byte shorter.

# **VAX Instruction Set MCOM**

# **MCOM**

Move Complemented

operand.

| FORMAT          | орс              | ode src.                                     | rx, dst.wx                                                             |

|-----------------|------------------|----------------------------------------------|------------------------------------------------------------------------|

| condition codes | N<br>Z<br>V<br>C | ← dst LSS 0;<br>← dst EQL 0;<br>← 0;<br>← C; |                                                                        |

| exceptions      |                  | Vone.                                        |                                                                        |

| opcodes         | 92<br>B2<br>D2   | MCOMB<br>MCOMW<br>MCOML                      | Move Complemented Byte  Move Complemented Word  Move Complemented Long |

| DESCRIPTION     | The              | destination ope                              | erand is replaced by the one's complement of the source                |

## **MNEG**

Move Negated

| FORMAT          | opc            | ode src.rx,                                                          | dst.wx                                                  |

|-----------------|----------------|----------------------------------------------------------------------|---------------------------------------------------------|

| condition codes | Z<br>V         | ← dst LSS 0;<br>← dst EQL 0;<br>← {integer overflow}<br>← dst NEQ 0; | <b>}</b> ;                                              |

| exceptions      | iı             | nteger overflow                                                      |                                                         |

| opcodes         | 8E<br>AE<br>CE | MNEGB<br>MNEGW<br>MNEGL                                              | Move Negated Byte  Move Negated Word  Move Negated Long |

### Note

**DESCRIPTION**

Integer overflow occurs if the source operand is the largest negative integer (which has no positive counterpart). On overflow, the destination operand is replaced by the source operand.

The destination operand is replaced by the negative of the source operand.

# **VAX Instruction Set MOV**

# MOV

Move

| FORMAT          | opco     | ode src.rx  | k, dst.wx |  |

|-----------------|----------|-------------|-----------|--|

| condition codes |          |             |           |  |

|                 |          | dst LSS 0;  |           |  |

|                 | Z +      | dst EQL 0;  |           |  |

|                 | V +      | <b>—</b> 0; |           |  |

|                 | C +      | — C;        |           |  |

| exceptions      | No       | one.        |           |  |

| opcodes         | <u> </u> |             |           |  |

| •               | 90       | MOVB        | Move Byte |  |

|                 | B0       | MOVW        | Move Word |  |

|                 | D0       | MOVL        | Move Long |  |

|                 | 7D       | MOVQ        | Move Quad |  |

|                 | 7DFD     | MOVO        | Move Octa |  |

**DESCRIPTION**

The destination operand is replaced by the source operand.

## **MOVZ**

**DESCRIPTION**

Move Zero-Extended

| FORMAT          | opc            | ode src.rx,                          | dst.wy                                                                                                |

|-----------------|----------------|--------------------------------------|-------------------------------------------------------------------------------------------------------|

| condition codes | Z<br>V         | ← 0;<br>← dst EQL 0;<br>← 0;<br>← C; |                                                                                                       |

| exceptions      | N.             | Vone.                                |                                                                                                       |

| opcodes         | 9B<br>9A<br>3C | MOVZBW<br>MOVZBL<br>MOVZWL           | Move Zero-Extended Byte to Word<br>Move Zero-Extended Byte to Long<br>Move Zero-Extended Word to Long |

For MOVZBW, bits 7:0 of the destination operand are replaced by the source operand; bits 15:8 are replaced by zero. For MOVZBL, bits 7:0 of the destination operand are replaced by the source operand; bits 31:8 are replaced by zero. For MOVZWL, bits 15:0 of the destination operand are

replaced by the source operand; bits 31:16 are replaced by zero.

# **VAX Instruction Set MUL**

## MUL

### Multiply

| FORMAT          | •        | erand:<br>erand: | opcode<br>opcode | mulr.rx, prod.mx<br>mulr.rx, muld.rx, prod.wx                           |

|-----------------|----------|------------------|------------------|-------------------------------------------------------------------------|

| condition codes | N        | ← prod LS        | S 0;             |                                                                         |

|                 | Z        | ← prod EC        | 0L 0;            |                                                                         |

|                 | V        | ←— {integer      | overflow};       |                                                                         |

|                 | С        | <b>←</b> 0;      |                  |                                                                         |

| exceptions      | ir.      | iteger over      | flow             |                                                                         |

|                 |          |                  |                  |                                                                         |

| opcodes         | 84       | MULB2            |                  | Multiply Byte 2 Operand                                                 |

| opcodes         | 84<br>85 | MULB2<br>MULB3   |                  | Multiply Byte 2 Operand Multiply Byte 3 Operand                         |

| opcodes         |          |                  |                  | Multiply Byte 2 Operand Multiply Byte 3 Operand Multiply Word 2 Operand |

| opcodes         | 85       | MULB3            |                  | Multiply Byte 3 Operand                                                 |

| opcodes         | 85<br>A4 | MULB3<br>MULW2   |                  | Multiply Byte 3 Operand<br>Multiply Word 2 Operand                      |

## **DESCRIPTION**

In 2 operand format, the product operand is multiplied by the multiplier operand, and the product operand is replaced by the low half of the double-length result. In 3 operand format, the multiplicand operand is multiplied by the multiplier operand, and the product operand is replaced by the low half of the double-length result.

#### Note

Integer overflow occurs if the high half of the double-length result is not equal to the sign extension of the low half of the double-length result.

# **PUSHL**

Push Long

| FORMAT          | opcode s                                         | src.rl    |  |

|-----------------|--------------------------------------------------|-----------|--|

| condition codes | N ← src LSS (<br>Z ← src EQL<br>V ← 0;<br>C ← C; |           |  |

| exceptions      | None.                                            |           |  |

| opcodes         | DD PUSHL                                         | Push Long |  |

### **DESCRIPTION**

The longword source operand is pushed on the stack.

- 1 PUSHL is equivalent to MOVL **src**, –(SP), but is 1 byte shorter.

- 2 POPL is not a VAX instruction. However, the assembler recognizes the inclusion of *POPL destination* in a program, for which it generates the code for *MOVL (SP)+*, destination.

# **VAX Instruction Set ROTL**

# **ROTL**

Rotate Long

| FORMAT          | opcode cnt.rb, src.rl, dst.wl               |   |

|-----------------|---------------------------------------------|---|

| condition codes | N ← dst LSS 0; Z ← dst EQL 0; V ← 0; C ← C; |   |

| exceptions      | None.                                       |   |

| opcodes         | 9C ROTL Rotate Lon                          | g |

### **DESCRIPTION**

The source operand is rotated logically by the number of bits specified by the count operand, and the destination operand is replaced by the result. The source operand is unaffected. A positive count operand rotates to the left. A negative count operand rotates to the right. A zero count operand replaces the destination operand with the source operand.

# **SBWC**

Subtract with Carry

| FORMAT          | opcode sub.rl, dif.ml                                                                         |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------|--|--|--|

| condition codes | N ← dif LSS 0; Z ← dif EQL 0; V ← {integer overflow}; C ← {borrow into most significant bit}; |  |  |  |

| exceptions      | integer overflow                                                                              |  |  |  |

| opcodes         | D9 SBWC Subtract with carry                                                                   |  |  |  |

### **DESCRIPTION**

The subtrahend operand and the contents of the condition code C-bit are subtracted from the difference operand, and the difference operand is replaced by the result.

- 1 On overflow, the difference operand is replaced by the low-order bits of the true result.

- 2 The two subtractions in the operation are performed simultaneously.

## **SUB**

### Subtract

| FORMAT          | •                | erand:<br>erand:                                  | opcode<br>opcode | sub.rx, dif.mx<br>sub.rx, min.rx, dif.wx        |

|-----------------|------------------|---------------------------------------------------|------------------|-------------------------------------------------|

| condition codes | N<br>Z<br>V<br>C | ← dif LSS<br>← dif EQL<br>← {integer<br>← {borrow | 0;               | cant bit};                                      |

| exceptions      | i                | nteger over                                       | flow             |                                                 |

| opcodes         | 82               | SUBB2                                             |                  | Subtract Byte 2 Operand                         |

|                 | 83<br>A2         | SUBB3<br>SUBW2                                    |                  | Subtract Byte 3 Operand Subtract Word 2 Operand |

|                 | А3               | SUBW3                                             |                  | Subtract Word 3 Operand                         |

|                 | C2               | SUBL2                                             |                  | Subtract Long 2 Operand                         |

|                 | C3               | SUBL3                                             |                  | Subtract Long 3 Operand                         |

## **DESCRIPTION**

In 2 operand format, the subtrahend operand is subtracted from the difference operand, and the difference operand is replaced by the result. In 3 operand format, the subtrahend operand is subtracted from the minuend operand, and the difference operand is replaced by the result.

### Note

Integer overflow occurs if the input operands to the subtract are of different signs and the sign of the result is the sign of the subtrahend. On overflow, the difference operand is replaced by the low-order bits of the true result.

| _ |  |

|---|--|

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

Test

| FORMAT          | opc            | ode src.rx                                   | <b>«</b>                            |  |

|-----------------|----------------|----------------------------------------------|-------------------------------------|--|

| condition codes | Z<br>V         | ← src LSS 0;<br>← src EQL 0;<br>← 0;<br>← 0; |                                     |  |

| exceptions      | N              | Vone.                                        |                                     |  |

| opcodes         | 95<br>B5<br>D5 | TSTB<br>TSTW<br>TSTL                         | Test Byte<br>Test Word<br>Test Long |  |

## **DESCRIPTION**

The condition codes are modified according to the value of the source operand.  $\ \ \,$

### Note

The operand **src** is equivalent to CMPx **src**, S^#0, but is 1 byte shorter.

# **VAX Instruction Set XOR**

# **XOR**

Exclusive OR

| FORMAT          | 2operano<br>3operano                                                                                                                                  | •                   | mask.rx, dst.mx<br>mask.rx, src.rx, dst.wx                                                                                                                              |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| condition codes | $\begin{array}{ccc} N & \longleftarrow \text{dst I} \\ Z & \longleftarrow \text{dst I} \\ V & \longleftarrow 0; \\ C & \longleftarrow C; \end{array}$ | •                   |                                                                                                                                                                         |

| exceptions      | None.                                                                                                                                                 |                     |                                                                                                                                                                         |

| opcodes         | 8C XORE<br>8D XORE<br>AC XORV<br>AD XORV<br>CC XORL<br>CD XORL                                                                                        | 23<br>V2<br>V3<br>2 | Exclusive OR Byte 2 Operand Exclusive OR Byte 3 Operand Exclusive OR Word 2 Operand Exclusive OR Word 3 Operand Exclusive OR Long 2 Operand Exclusive OR Long 3 Operand |

## **DESCRIPTION**

In 2 operand format, the result of the logical XOR on the mask operand and the destination operand replaces the destination operand. In 3 operand format, the result of the logical XOR on the mask operand and the source operand replaces the destination operand.

## 9.2.2 Address Instructions

The following instructions are described in this section.

|    | Description and Opcode                                   | Number of<br>Instructions |

|----|----------------------------------------------------------|---------------------------|

| 1. | Move Address<br>MOVA{B,W,L=F,Q=D=G,O=H} src.ax, dst.wl   | 5                         |

| 2. | Push Address PUSHA{B,W,L=F,Q=D=G,O=H} src.ax, {-(SP).wl} | 5                         |

# **VAX Instruction Set MOVA**

## **MOVA**

Move Address

| FORMAT          | opcode src.ax, dst.wl |                                              |                                      |

|-----------------|-----------------------|----------------------------------------------|--------------------------------------|

| condition codes | Z                     | — dst LSS 0;<br>— dst EQL 0;<br>— 0;<br>— C; |                                      |

| exceptions      | No                    | one.                                         |                                      |

| opcodes         | 9E                    | MOVAB                                        | Move Address Byte                    |

|                 | 3E                    | MOVAW                                        | Move Address Byte  Move Address Word |

|                 | DE                    | MOVAL                                        | Move Address Long                    |

|                 |                       | MOVAF                                        | Move Address F_floating              |

|                 | 7E                    | MOVAQ                                        | Move Address Quad                    |

|                 |                       | MOVAD                                        | Move Address D_floating              |

|                 |                       | MOVAG                                        | Move Address G_floating              |

|                 | 7EFD                  | MOVAH                                        | Move Address H_floating              |

|                 |                       | MOVAO                                        | Move Address Octa                    |

# **DESCRIPTION**

The destination operand is replaced by the source operand. The context in which the source operand is evaluated is given by the data type of the instruction. The operand whose address replaces the destination operand is not referenced.

### Note

The access type of the source operand is address, which causes the address of the specified operand to be moved.

## **PUSHA**

Push Address

| FORMAT          | орсс                                        | de src.ax                                                      |                                                                                                                                                                                              |  |

|-----------------|---------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| condition codes | N ← src LSS 0; Z ← src EQL 0; V ← 0; C ← C; |                                                                |                                                                                                                                                                                              |  |

| exceptions      | No                                          | one.                                                           |                                                                                                                                                                                              |  |

| opcodes         | 9F<br>3F<br>DF<br>7F<br>7FFD                | PUSHAB PUSHAW PUSHAL PUSHAF PUSHAQ PUSHAD PUSHAG PUSHAH PUSHAO | Push Address Byte Push Address Word Push Address Long, Push Address F_floating Push Address Quad, Push Address D_floating, Push Address G_floating Push Address H_floating Push Address Octa |  |

### **DESCRIPTION**

The source operand is pushed on the stack. The context in which the source operand is evaluated is given by the data type of the instruction. The operand whose address is pushed is not referenced.

- 1 PUSHAx **src** is equivalent to MOVAx **src**, –(SP), but is one byte shorter.

- 2 The source operand is of address access type, which causes the address of the specified operand to be pushed.

# VAX Instruction Set PUSHA

## 9.2.3 Variable-Length Bit Field Instructions

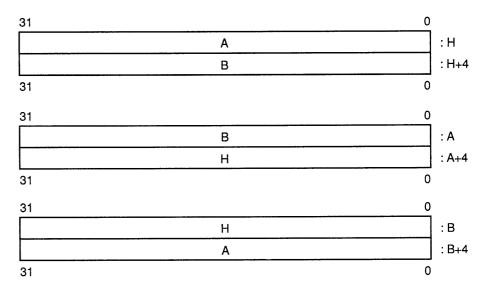

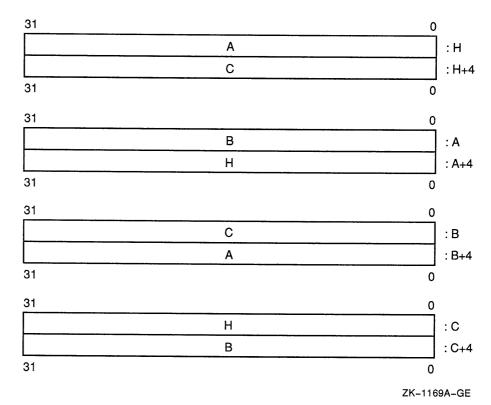

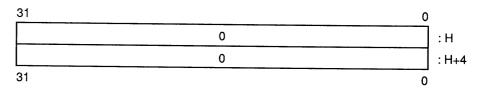

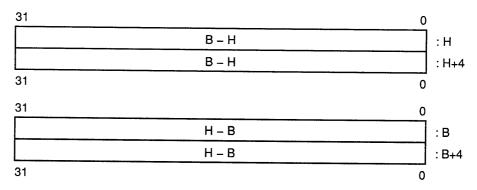

A variable-length bit field is specified by the following three operands:

- 1 A longword position operand.

- **2** A byte field size operand in the range 0 to 32; if out of this range, a reserved operand fault occurs.

- A base address. Use the position operand to locate the bit field relative to this base address. The address is obtained from an operand of address access type. However, unlike other instances of operand specifiers of address access type, register mode can be designated in the operand specifier. In this case, the field is contained in the register n designated by the operand specifier (or register n+1 concatenated with register n). (See Chapter 8.) If the field is contained in a register and the size operand is not zero, the position operand must have a value in the range 0 to 31, or a reserved operand fault occurs.

Zero bytes are referenced if the field size is zero.

The following instructions are described in this section.

|    | Description and Opcode                                                         | Number of<br>Instructions |

|----|--------------------------------------------------------------------------------|---------------------------|

| 1. | Compare Field CMPV pos.rl, size.rb, base.vb, {field.rv}, src.rl                | 1                         |

| 2. | Compare Zero-Extended Field CMPZV pos.rl, size.rb, base.vb, {field.rv}, src.rl | 1                         |

| 3. | Extract Field EXTV pos.rl, size.rb, base.vb, {field.rv}, dst.wl                | 1                         |

| 4. | Extract Zero-Extended Field EXTZV pos.rl, size.rb, base.vb, {field.rv}, dst.wl | 1                         |

| 5. | Find First FF{S,C} startpos.rl, size.rb, base.vb, {field.rv}, findpos.wl       | 2                         |

| 6. | Insert Field INSV src.rl, pos.rl, size.rb, base.vb, {field.wv}                 | 1                         |

# VAX Instruction Set PUSHA

The following variable-length bit field instructions are described in Section 9.2.4:

|    | Description and Opcode                                                                          | Number of<br>Instructions |

|----|-------------------------------------------------------------------------------------------------|---------------------------|

| 1. | Branch on Bit<br>BB{S,C} pos.rl, base.vb, displ.bb,<br>{field.rv}                               | 2                         |

| 2. | Branch on Bit (and modify without interlock) BB{S,C}{S,C} pos.rl, base.vb, displ.bb, {field.mv} | 4                         |

| 3. | Branch on Bit (and modify) Interlocked BB{SS,CC}I pos.rl, base.vb, displ.bb, {field.mv}         | 2                         |

# VAX Instruction Set CMP

# **CMP**

Compare Field

| FORMAT          | opcode                                                                      | pos.rl, size.rb, base.vb, src.rl          |  |  |  |

|-----------------|-----------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| condition codes | Condition codes  N ← tmp LSS src; Z ← tmp EQL src; V ← 0; C ← tmp LSSU src; |                                           |  |  |  |

| exceptions      | reserved o                                                                  | perand                                    |  |  |  |

| opcodes         | EC CMPV<br>ED CMPZV                                                         | Compare Field Compare Zero-Extended Field |  |  |  |

## **DESCRIPTION**

The field specified by the position, size, and base operands is compared with the source operand. For CMPV, the source operand is compared with the sign-extended field. For CMPZV, the source operand is compared with the zero-extended field. The only action is to affect the condition codes.

- 1 A reserved operand fault occurs if:

- size GTRU 32

- **pos** GTRU 31, **size** NEQ 0, and the field is contained in the registers

- 2 On a reserved operand fault, the condition codes are UNPREDICTABLE.

# **EXT**

#### Extract Field

| FORMAT          | opcode pos.rl, siz                                   | e.rb, base.vb, dst.wl                     |  |  |  |

|-----------------|------------------------------------------------------|-------------------------------------------|--|--|--|

| condition codes | N ← dst LSS 0;<br>Z ← dst EQL 0;<br>V ← 0;<br>C ← C; |                                           |  |  |  |

| exceptions      | reserved operand                                     |                                           |  |  |  |

| opcodes         | EE EXTV<br>EF EXTZV                                  | Extract Field Extract Zero-Extended Field |  |  |  |

## **DESCRIPTION**

For EXTV, the destination operand is replaced by the sign-extended field specified by the position, size, and base operands. For EXTZV, the destination operand is replaced by the zero-extended field specified by the position, size, and base operands. If the size operand is zero, the only action is to replace the destination operand with zero and to modify the condition codes.

- 1 A reserved operand fault occurs if:

- size GTRU 32

- **pos** GTRU 31, **size** NEQ 0, and the field is contained in the registers

- 2 On a reserved operand fault, the destination operand is unaffected, and the condition codes are UNPREDICTABLE.

|   | _ |

|---|---|

|   |   |

| _ | _ |

|   | • |

Find First

| FORMAT          | opcode s                                     | startpos.rl, size.rb, base.vb, findpos.wl |

|-----------------|----------------------------------------------|-------------------------------------------|

| condition codes | N ← 0;<br>Z ← {bit not ·<br>V ← 0;<br>C ← 0; | found};                                   |

| exceptions      | reserved ope                                 | erand                                     |

| opcodes         | EB FFC<br>EA FFS                             | Find First Clear<br>Find First Set        |

## **DESCRIPTION**

A field specified by the start position, size, and base operands is extracted. Starting at bit 0 and extending to the highest bit in the field, the field is tested for a bit in the state indicated by the instruction. If a bit in the indicated state is found, the find position operand is replaced by the position of the bit, and the Z condition code bit is cleared. If no bit in the indicated state is found, the find position operand is replaced by the position (relative to the base) of a bit one position to the left of the specified field, and the Z condition code bit is set. If the size operand is zero, the find position operand is replaced by the start position operand, and the Z condition code bit is set.

- 1 A reserved operand fault occurs if:

- size GTRU 32

- **startpos** GTRU 31, **size** NEQ 0, and the field is contained in the registers

- 2 On a reserved operand fault, the find position operand is unaffected, and the condition codes are UNPREDICTABLE.

# INSV

Insert Field

| FORMAT          | opcode src.rl                                                                                                                     | rl, pos.rl, size.rb, base.vb |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|

| condition codes | $\begin{array}{lll} N & \longleftarrow N; \\ Z & \longleftarrow Z; \\ V & \longleftarrow V; \\ C & \longleftarrow C; \end{array}$ |                              |  |

| exceptions      | reserved operand                                                                                                                  | d                            |  |

| opcodes         | F0 INSV                                                                                                                           | Insert Field                 |  |

## **DESCRIPTION**

The field specified by the position, size, and base operands is replaced by bits size-1:0 of the source operand. If the size operand is zero, the instruction has no effect.

- 1 A reserved operand fault occurs if:

- size GTRU 32

- **pos** GTRU 31, **size** NEQ 0, and the field is contained in the registers

- 2 On a reserved operand fault, the field is unaffected, and the condition codes are UNPREDICTABLE.

# 9.2.4 Control Instructions

In most implementations of the VAX architecture, improved execution speed will result if the target of a control instruction is on an aligned longword boundary.

The following instructions are described in this section.

|    | Description a                                                                                                                     | and Opcode                                           | Number of<br>Instructions |

|----|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------|

| 1. | Add Compare and Branch ACB{B,W,L,F,D,G,H} limit.rx, add.rx, index.mx, displ.bw Compare is LE on positive add, GE on negative add. |                                                      | 7                         |

| 2. |                                                                                                                                   | Branch Less Than or Equal<br>.rl, index.ml, displ.bb | 1                         |

| 3. |                                                                                                                                   | Branch Less Than<br>rl, index.ml, displ.bb           | 1                         |

| 4. | Conditional Br                                                                                                                    | anch                                                 | 12                        |

|    | Condition                                                                                                                         |                                                      |                           |

|    | LSS                                                                                                                               | Less Than                                            |                           |

|    | LEQ                                                                                                                               | Less Than or Equal                                   |                           |

|    | EQL, EQLU                                                                                                                         | Equal, Equal Unsigned                                |                           |

|    | NEQ, NEQU                                                                                                                         | Not Equal, Not Equal Unsigned                        |                           |

|    | GEQ                                                                                                                               | Greater Than or Equal                                |                           |

|    | GTR                                                                                                                               | Greater Than                                         |                           |

|    | LSSU, CS                                                                                                                          | Less Than Unsigned, Carry Set                        |                           |

|    | LEQU                                                                                                                              | Less Than or Equal Unsigned                          |                           |

|    | GEQU, CC                                                                                                                          | Greater Than or Equal Unsigned,<br>Carry Clear       |                           |

|    | GTRU                                                                                                                              | Greater Than Unsigned                                |                           |

|    | VS                                                                                                                                | Overflow Set                                         |                           |

|    | VC                                                                                                                                | Overflow Clear                                       | ····                      |

| 5. | Branch on Bit BB{S,C} pos.rl, base.vb, displ.bb, {field.rv}                                                                       |                                                      | 2                         |

| 6. | Branch on Bit (and modify without interlock) BB{S,C}{S,C} pos.rl, base.vb, displ.bb, {field.mv}                                   |                                                      | 4                         |

| 7. | Branch on Bit (BB{SS,CC}I po                                                                                                      | 2                                                    |                           |

# VAX Instruction Set INSV

|     | Description and Opcode                                                            | Number of<br>Instructions |

|-----|-----------------------------------------------------------------------------------|---------------------------|

| 8.  | Branch on Low Bit<br>BLB{S,C} src.rl, displ.bb                                    | 2                         |

| 9.  | Branch with {Byte, Word} Displacement BR{B,W} displ.bx                            | 2                         |

| 10. | Branch to Subroutine with {Byte, Word} Displacement BSB{B,W} displ.bx, {-(SP).wl} | 2                         |

| 11. | Case CASE{B,W,L} selector.rx, base.rx, limit.rx, displ.bw-list                    | 3                         |

| 12. | Jump<br>JMP dst.ab                                                                | 1                         |

| 13. | Jump to Subroutine<br>JSB dst.ab, {-(SP).wl}                                      | 1                         |

| 14. | Return from Subroutine RSB {(SP)+.rl}                                             | 1                         |

| 15. | Subtract One and Branch Greater Than or Equal SOBGEQ index.ml, displ.bb           | 1                         |

| 16. | Subtract One and Branch Greater Than SOBGTR index.ml, displ.bb                    | 1                         |

## **ACB**

Add Compare and Branch

| FORMAT          | opcode limit.rx, add.rx, index.mx, displ.bw                                     |                       |                                                          |

|-----------------|---------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------|

| condition codes |                                                                                 |                       |                                                          |

|                 | N -                                                                             | ← index LSS 0;        |                                                          |

|                 | Z ·                                                                             | ← index EQL 0;        |                                                          |

|                 | ٧ .                                                                             | ← {integer overflow}; |                                                          |

|                 | C ·                                                                             | ← C;                  |                                                          |

| exceptions      | integer overflow<br>floating overflow<br>floating underflow<br>reserved operand |                       |                                                          |

| opcodes         | 9D                                                                              | ACBB                  | Add Compare and Drazak Data                              |

|                 | 3D                                                                              | ACBW                  | Add Compare and Branch Byte  Add Compare and Branch Word |

|                 | F1                                                                              | ACBL                  | Add Compare and Branch Long                              |

|                 | 4F                                                                              | ACBF                  | Add Compare and Branch F_floating                        |

|                 | 4FFD                                                                            | ACBG                  | Add Compare and Branch G_floating                        |

|                 | 6F                                                                              | ACBD                  | Add Compare and Branch D_floating                        |

|                 |                                                                                 |                       | noo oompare and branch b_hoating                         |

# **DESCRIPTION**

The addend operand is added to the index operand and the index operand is replaced by the result. The index operand is compared with the limit operand. If the addend operand is positive (or zero) and the comparison is less than or equal to zero, or if the addend is negative and the comparison is greater than or equal to zero, the sign-extended branch displacement is added to the program counter (PC), and the PC is replaced by the result.

- 1 ACB efficiently implements the general FOR or DO loops in high-level languages, since the sense of the comparison between **index** and **limit** is dependent on the sign of the addend.

- 2 On integer overflow, the index operand is replaced by the low-order bits of the true result. Comparison and branch determination proceed normally on the updated index operand.

- 3 On floating underflow, if FU is clear, the index operand is replaced by zero, and comparison and branch determination proceed normally. A fault occurs if FU is set, and the index operand is unaffected.

# VAX Instruction Set ACB

- 4 On floating overflow, the instruction takes a floating overflow fault, and the index operand is unaffected.

- 5 On a reserved operand fault, the index operand is unaffected, and condition codes are UNPREDICTABLE.

- 6 Except for the circumstance described in note 5, the C-bit is unaffected.

# **AOBLEQ**

Add One and Branch Less Than or Equal

| FORMAT          | opcode limit.rl, index.ml, displ.bb                              |

|-----------------|------------------------------------------------------------------|

| condition codes | N ← index LSS 0; Z ← index EQL 0; V ← {integer overflow}; C ← C; |

| exceptions      | integer overflow                                                 |

| opcodes         | F3 AOBLEQ Add One and Branch Less Than or Equal                  |

### **DESCRIPTION**

One is added to the index operand, and the index operand is replaced by the result. The index operand is compared with the limit operand. If the comparison is less than or equal to zero, the sign-extended branch displacement is added to the program counter (PC), and the PC is replaced by the result.

- 1 Integer overflow occurs if the index operand before addition is the largest positive integer. On overflow, the index operand is replaced by the largest negative integer, and the branch is taken.

- 2 The C-bit is unaffected.

## **AOBLSS**

Add One and Branch Less Than

| FORMAT          | opcode limit.rl, index.ml, displ.bb                              |  |  |  |  |

|-----------------|------------------------------------------------------------------|--|--|--|--|

| condition codes | N ← index LSS 0; Z ← index EQL 0; V ← {integer overflow}; C ← C; |  |  |  |  |

| exceptions      | integer overflow                                                 |  |  |  |  |

| opcodes         | F2 AOBLSS Add One and Branch Less Than                           |  |  |  |  |

### **DESCRIPTION**

One is added to the index operand and the index operand is replaced by the result. The index operand is compared with the limit operand. If the comparison result is less than zero, the sign-extended branch displacement is added to the program counter (PC), and the PC is replaced by the result.

- 1 Integer overflow occurs if the index operand before addition is the largest positive integer. On overflow, the index operand is replaced by the largest negative integer, and thus (unless the limit operand is the largest negative integer), the branch is taken.

- 2 The C-bit is unaffected.

# B

Branch on (condition)

| FORMAT          | opo              | code displ.bb                |                |                                                           |

|-----------------|------------------|------------------------------|----------------|-----------------------------------------------------------|

| condition codes | N<br>Z<br>V<br>C | ← N;<br>← Z;<br>← V;<br>← C; |                |                                                           |

| exceptions      | 1                | Vone.                        |                |                                                           |

| opcodes         | 14               | {N OR Z} EQL 0               | BGTR           | Branch on Greater Than (signed)                           |

|                 | 15               | {N OR Z} EQL 1               | BLEQ           | Branch on Less Than or Equal (signed)                     |

|                 | 12               | Z EQL 0                      | BNEQ,<br>BNEQU | Branch on Not Equal (signed) Branch on Not Equal Unsigned |

|                 | 13               | Z EQL 1                      | BEQL,<br>BEQLU | Branch on Equal (signed) Branch on Equal Unsigned         |

|                 | 18               | N EQL 0                      | BGEQ           | Branch on Greater Than or Equal (signed)                  |

|                 | 19               | N EQL 1                      | BLSS           | Branch on Less Than (signed)                              |

|                 | 1A               | (C OR Z) EQL 0               | BGTRU          | Branch on Greater Than Unsigned                           |

|                 | 1B               | (C OR Z) EQL 1               | BLEQU          | Branch Less Than or Equal Unsigned                        |

|                 | 1C               | V EQL 0                      | BVC            | Branch on Overflow Clear                                  |

|                 | 1D               | V EQL 1                      | BVS            | Branch on Overflow Set                                    |

|                 | 1E               | C EQL 0                      | BGEQU,         | Branch on Greater Than or Equal Unsigned                  |

|                 |                  |                              | BCC            | Branch on Carry Clear                                     |

|                 | 1F               | C EQL 1                      | BLSSU,         | Branch on Less Than Unsigned                              |

|                 |                  |                              | BCS            | Branch on Carry Set                                       |

# **DESCRIPTION**

The condition codes are tested. If the condition indicated by the instruction is met, the sign-extended branch displacement is added to the program counter (PC), and the PC is replaced by the result.

#### **Notes**

The VAX conditional branch instructions permit considerable flexibility in branching but require care in choosing the correct branch instruction. The conditional branch instructions are best seen as three overlapping groups:

#### 1 Overflow and Carry Group

| BVS | V EQL 1 |

|-----|---------|

| BVC | V EQL 0 |

| BCS | C EQL 1 |

| BCC | C EQL 0 |

Typically, you would use these instructions to check for overflow (when overflow traps are not enabled), for multiprecision arithmetic, and for other special purposes.